# **Sh.D** Thesis

# An Error-Localization, Validation and Optimization Tool for Embedded Code Augmentation: an Architecture Oriented Approach

# Submitted to Cochin University of Science and Technology

In partial fulfillment of the requirements for the award of the degree of

# **Doctor of Philosophy**

# бу MARIAMMA CHACKO

Under the guidance of **Dr. K. POULOSE JACOB**

# DEPARTMENT OF COMPUTER SCIENCE FACULTY OF TECHNOLOGY COCHIN UNIVERSITY OF SCIENCE AND TECHNOLOGY COCHIN, INDIA 682 022

August 2011

# An Error-Localization, Validation and Optimization Tool for Embedded Code Augmentation: an Architecture Oriented Approach

Ph.D Thesis in the field of Embedded Systems

#### Author

#### MARIAMMA CHACKO

Department of Computer Science Cochin University of Science and Technology Cochin, Kerala, India 682 022 Email: mariamma@cusat.ac.in

# **Research Advisor**

# Dr. K. POULOSE JACOB

Professor Department of Computer Science Cochin University of Science and Technology Cochin, Kerala, India 682 022 Email: kpj@cusat.ac.in

August 2011

"Yea, though I walk through the valley of the shadow of death, I will fear no evil: for thou art with me; thy rod and thy staff they comfort me".

Holy Bible, Psalms: 23:4

*Lovingly dedicated to my parents,* Husband and daughters

# CERTIFICATE

This is to certify that this thesis entitled "An Error-Localization, Validation and Optimization Tool for Embedded Code Augmentation: an Architecture Oriented Approach" is a bona fide record of the research work carried out by Mrs. Mariamma Chacko under my supervision in the Department of Computer Science, Cochin University of Science and Technology. The results presented in this thesis or parts of it have not been presented for the award of any other degree(s).

Dr. K. Poulose Jacob

(Supervising Guide) Professor Department of Computer Science Cochin University of Science and Technology

Cochin 22 22-08-2011

#### **DECLARATION**

I hereby declare that the work presented in this thesis entitled "*An Error-Localization, Validation and Optimization Tool for Embedded Code Augmentation: an Architecture Oriented Approach*" is based on the original research work carried out by me under the supervision of **Dr. K. Poulose Jacob**, Professor, in the Department of Computer Science, Cochin University of Science and Technology. The results presented in this thesis or parts of it have not been presented for the award of any other degree.

MARIAMMA CHACKO

Cochin 22 22-08-2011

# ACKNOWLEDGEMENTS

I would like to express my heartfelt gratitude to my research guide Dr. K. Poulose Jacob, Professor & Head of the Department, Department of Computer Science, Cochin University of Science and Technology for his guidance, support and timely advice. I could not have completed the thesis without his encouragement and valuable suggestions.

My heartfelt debt and thanks goes to my teachers and former heads of the department of Electronics Prof. (Dr) K. G. Nair, Prof. (Dr) C. S. Sridhar and Prof. (Dr) K. G. Balakrishnan, for their advice and encouragement during the past years.

I would like to acknowledge the support provided by all my colleagues in the department of Ship Technology.

I thank the entire library, technical and administrative staff of the department of Computer Science as well as the department of Ship Technology for their co-operation and support.

My special thanks to the doctors who have treated me during my adverse health conditions and to my friend Mrs. Santha Roy for her love and companionship during these years.

Let me also remember at this moment the co-operation provided by my daughters during these years.

I would like to thank all of the people who have helped, encouraged and supported me directly or indirectly during the period of my research work.

Finally, and most of all, I would like to thank my husband James for his love, support, guidance and understanding without whom completion of this dissertation would not have been possible.

# ABSTRACT

# An Error-Localization, Validation and Optimization Tool for Embedded Code Augmentation: an Architecture Oriented Approach

Embedded systems are usually designed for a single or a specified set of tasks. This specificity means the system design as well as its hardware/software development can be highly optimized. Embedded software must meet the requirements such as high reliability operation on resource-constrained platforms, real time constraints and rapid development. This necessitates the adoption of static machine codes analysis tools running on a host machine for the validation and optimization of embedded system codes, which can help meet all of these goals. This could significantly augment the software quality and is still a challenging field.

This dissertation contributes to an architecture oriented code validation, error localization and optimization technique assisting the embedded system designer in software debugging, to make it more effective at early detection of software bugs that are otherwise hard to detect, using the static analysis of machine codes. The focus of this work is to develop methods that automatically localize faults as well as optimize the code and thus improve the debugging process as well as quality of the code.

Validation is done with the help of rules of inferences formulated for the target processor. The rules govern the occurrence of illegitimate/out of place instructions and code sequences for executing the computational and integrated

peripheral functions. The stipulated rules are encoded in propositional logic formulae and their compliance is tested individually in all possible execution paths of the application programs. An incorrect sequence of machine code pattern is identified using slicing techniques on the control flow graph generated from the machine code.

An algorithm to assist the compiler to eliminate the redundant bank switching codes and decide on optimum data allocation to banked memory resulting in minimum number of bank switching codes in embedded system software is proposed. A relation matrix and a state transition diagram formed for the active memory bank state transition corresponding to each bank selection instruction is used for the detection of redundant codes. Instances of code redundancy based on the stipulated rules for the target processor are identified.

This validation and optimization tool can be integrated to the system development environment. It is a novel approach independent of compiler/assembler, applicable to a wide range of processors once appropriate rules are formulated. Program states are identified mainly with machine code pattern, which drastically reduces the state space creation contributing to an improved state-of-the-art model checking. Though the technique described is general, the implementation is architecture oriented, and hence the feasibility study is conducted on PIC16F87X microcontrollers. The proposed tool will be very useful in steering novices towards correct use of difficult microcontroller features in developing embedded systems.

# <u>Contents</u>

| Abstract                                                    | X111  |

|-------------------------------------------------------------|-------|

| List of Tables                                              | xix   |

| List of Figures                                             | xxi   |

| Abbreviations                                               | xxiii |

| Chapter 1 INTRODUCTION                                      | 1-15  |

| 1.1 Background and Motivation                               | 2     |

| 1.1.1 Reliable Software                                     | 3     |

| 1.1.2 Redundant Codes                                       | 4     |

| 1.1.3 Software Constraints                                  | 5     |

| 1.2 Embedded System Development                             | 6     |

| 1.2.1 Real Time Systems                                     | 9     |

| 1.3 Validation and Optimization Techniques                  | 10    |

| 1.4 Programmable System on Chip (PSoC)                      | 12    |

| 1.5 Thesis Roadmap                                          | 13    |

| 1.6 Summary                                                 | 15    |

| Chapter 2 REVIEW OF DEBUGGING AND OPTIMIZATION TECHNOLOGIES | 17-69 |

| 2.1 Embedded System Constraints                             | 18    |

| 2.2 Software Development Tools                              | 21    |

| 2.2.1Embedded Software                                      | 23    |

| 2.2.1.1 Assemblers and Compilers                            | 25    |

| 2.2.1.2 Dependable Software                                 | 28    |

| 2.2.1.3 Emerging Technologies                               | 30    |

| 2.2.2 Fault Localization Techniques                         | 30    |

| 2.2.2.1 Source Level Debugger                               | 34    |

| 2.2.2.2 Program Slicing                                     | 36    |

| 2.2.2.3 Static Analysis Tools                               | 39    |

| 2.2.2.4 Static Analysis of Executables                      | 42    |

| 2.2.2.5 Static Analysis of Embedded Software      | 47     |

|---------------------------------------------------|--------|

| 2.2.2.6 Dynamic Analysis                          | 48     |

| 2.2.3 Debugging Systems and Tools                 | 50     |

| 2.2.3.1 Testing on Host Machine                   | 52     |

| 2.2.3.2 Simulator                                 | 53     |

| 2.2.3.3 Oscilloscopes and Logic Analyzers         | 53     |

| 2.2.3.4 In-Circuit Emulators                      | 54     |

| 2.2.3.5 On-Chip Debuggers                         | 55     |

| 2.3 Hardware and Software Integration             | 56     |

| 2.4 Control Flow Checking                         | 58     |

| 2.5 Optimization                                  | 60     |

| 2.5.1General Optimizations                        | 62     |

| 2.5.2 Processor Specific Optimizations            | 64     |

| 2.5.3 Interprocedural Optimizations               | 65     |

| 2.5.4 Profile-Guided Optimizations                | 66     |

| 2.5.5 Optimization of Bank Switching Instructions | 66     |

| 2.6 Summary                                       | 69     |

| Chapter 3 METHODOLOGY                             | 71-78  |

| 3.1 Program Partitioning                          | 71     |

| 3.2 Rule Formation and Codification               | 73     |

| 3.3 Validation and Fault Localization             | 74     |

| 3.4 Optimization                                  | 75     |

| 3.5 System Realization                            | 76     |

| 3.6 The Development Support Systems               | 77     |

| 3.7 Summary                                       | 78     |

| Chapter 4 CODE VALIDATION AND ERROR LOCALIZATION  | 79-120 |

| 4.1Validation Technique                           | 81     |

| 4.1.1Background                                  | 82      |

|--------------------------------------------------|---------|

| 4.1.2 Applicability in RISC Architectures        | 87      |

| 4.1.3 Control Flow Graph Construction            | 87      |

| 4.1.4 Codification of Rules                      | 90      |

| 4.1.5 Analysis Technique                         | 92      |

| 4.2 Tool Chain                                   | 96      |

| 4.3 Feasibility Study on PIC16F87X MCU           | 97      |

| 4.4. Code Validation and Error Detection         | 99      |

| 4.4.1Fault Localization                          | 99      |

| 4.4.2 Fault Diagnosis                            | 109     |

| 4.4.2.1 Discrepancy in the Opcodes or Operands   | 109     |

| 4.4.2.2 Illegal Opcodes                          | 110     |

| 4.4.2.3 Missed Instructions                      | 112     |

| 4.4.2.4 A Deadlock                               | 116     |

| 4.4.3 Error Correction                           | 117     |

| 4.5 Results and Discussions                      | 118     |

| 4.6 Summary                                      | 120     |

| Chapter 5 CODE OPTIMIZATION                      | 121-150 |

| 5.1. Motivation and Approach                     | 123     |

| 5.2. Detection of Redundant Bank Switching Codes | 126     |

| 5.2.1Relation Matrix Formulation                 | 128     |

| 5.2.2 Realization                                | 132     |

| 5.2.3 Tool Evaluation                            | 136     |

| 5.3 Optimization Technique                       | 141     |

| 5.3.1 Variable Partitioning                      | 141     |

| 5.3.2 Optimum Memory Bank Allocation             | 143     |

| 5.4 Redundant I/O port Configuration             | 147     |

| 5.5 Redundant ADC Channel Selection | 148     |

|-------------------------------------|---------|

| 5.6 Software Realization            | 149     |

| 5.7 Summary.                        | 150     |

| Chapter 6 CONCLUSIONS               | 151-159 |

| 6.1Contributions                    | 151     |

| 6.2 Highlights of the Work          | 153     |

| 6.3 Merits and Demerits             | 154     |

| 6.4 New Research Directions         | 158     |

| 6.5 Summary                         | 158     |

| REFERENCES                          | 161-175 |

| LIST OF PUBLICATIONS                | 177-178 |

| INDEX                               | 179-182 |

| APPENDIX- A                         | A1- A4  |

# LIST OF TABLES

| Table 4.1 | A-clusters for instructions MOV C, E; ADD B & POP B                                                                                  |     |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| Table 4.2 | Examples of (a) B-Cluster and & (b) C- Cluster                                                                                       | 84  |  |  |

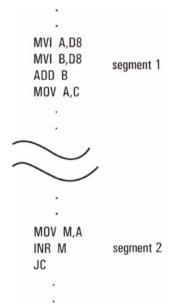

| Table 4.3 | A sample assembly language program used to describe the partitioning concepts and analysis of the proposed code validation technique | 94  |  |  |

| Table 4.4 | (a) to (i) List of governing rules formed for the PIC16F87X microcontrollers                                                         | 101 |  |  |

| Table 4.5 | Code sequence governing rule 1 of Table 4.4(c)                                                                                       | 113 |  |  |

| Table 4.6 | Code sequence governing rule 2 of table 4.4(a)                                                                                       | 114 |  |  |

| Table 4.7 | A delay program and its erroneous version resulting in a deadlock                                                                    | 117 |  |  |

| Table 5.1 | Bank switching instructions and their symbols                                                                                        | 129 |  |  |

| Table 5.2 | Relation matrix formation with PAMB and bank switching<br>instructions                                                               | 130 |  |  |

| Table 5.3 | Results of the analysis                                                                                                              | 140 |  |  |

| Table A.1 | Evaluation of programs developed using different compilers/assemblers                                                                | A3  |  |  |

# LIST OF FIGURES

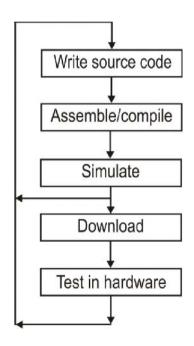

| Possible stages in the development process for the program of a 7 simple embedded system project.                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

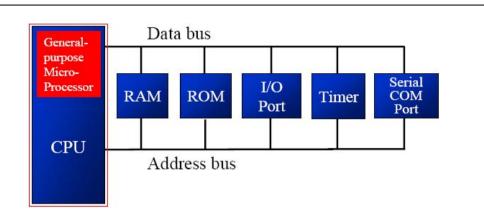

| The architectural differences between (a) general purpose microprocessor system and (b) a microcontroller (single chip).                                                                                                                                                                                                                                                                                                                                               | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

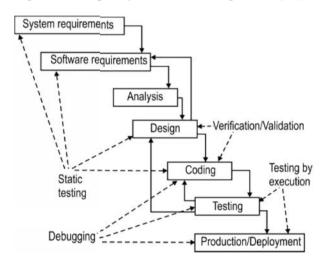

| Activities that involve testing, debugging, verification/ validation in a typical software development process.                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

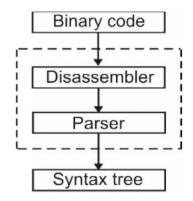

| Construction of the syntax tree from the binary code of a program.                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

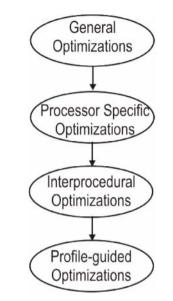

| A typical optimization sequence in an advanced compiler.                                                                                                                                                                                                                                                                                                                                                                                                               | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

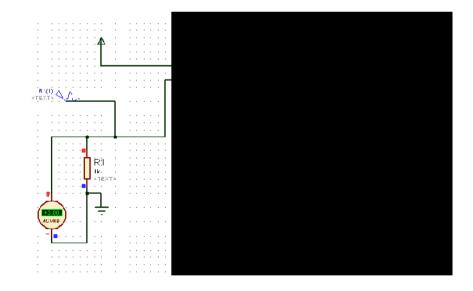

| A sample design developed for simulation using PROTEUS VSM for a traffic signaling application based on PIC16F877 microcontroller.                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

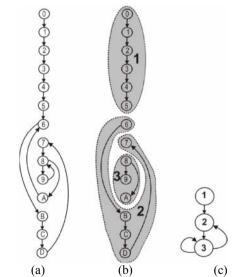

| CFG abstraction details for the sample program given in Table 4.3. (a) shows the program graph, (b) shows the formation of subprograms <b>1</b> , <b>2</b> and <b>3</b> by eliminating the incoming arcs of the merge nodes 6 and 8 whereas (c) shows the CFG.                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

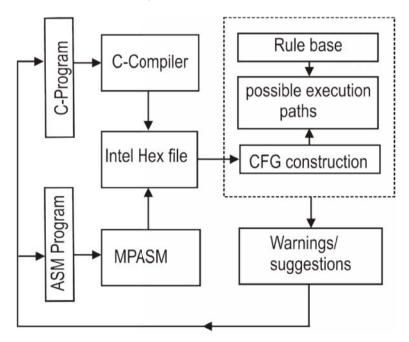

| The tool chain used for the proposed validation technique of embedded system machine codes.                                                                                                                                                                                                                                                                                                                                                                            | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Screen shots for the analysis and reporting of violation of sleep mode<br>operation of ADC if any. (a) the rule is validated when the antecedent<br>(0x0063immediately follows0x151F) of the formula is found true at<br>addresses 24h and 25h preceded by the consequent (0x179F and<br>0x171F) satisfied at addresses 1Bh and 1Ch. (b) reports the violation of<br>the rule as the antecedent is true at locations 4Bh and 4Ch without<br>satisfying its consequent. | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | simple embedded system project.<br>The architectural differences between (a) general purpose<br>microprocessor system and (b) a microcontroller (single chip).<br>Activities that involve testing, debugging, verification/ validation in a<br>typical software development process.<br>Construction of the syntax tree from the binary code of a program.<br>A typical optimization sequence in an advanced compiler.<br>A sample design developed for simulation using PROTEUS VSM for a<br>traffic signaling application based on PIC16F877 microcontroller.<br>CFG abstraction details for the sample program given in Table 4.3. (a)<br>shows the program graph, (b) shows the formation of subprograms <b>1</b> , <b>2</b><br>and <b>3</b> by eliminating the incoming arcs of the merge nodes 6 and 8<br>whereas (c) shows the CFG.<br>The tool chain used for the proposed validation technique of embedded<br>system machine codes.<br>Screen shots for the analysis and reporting of violation of sleep mode<br>operation of ADC if any. (a) the rule is validated when the antecedent<br>(0x0063immediately follows0x151F) of the formula is found true at<br>addresses 24h and 25h preceded by the consequent (0x179F and<br>0x171F) satisfied at addresses 1Bh and 1Ch. (b) reports the violation of<br>the rule as the antecedent is true at locations 4Bh and 4Ch without |  |  |

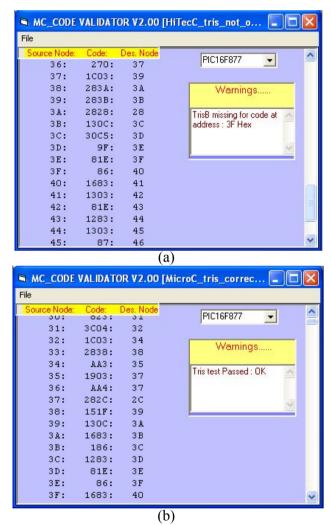

| Fig. 4.4 | Screenshots for the results of the analysis for TRISB register configuring | 115 |

|----------|----------------------------------------------------------------------------|-----|

|          | for programs developed in high level languages. (a) in the erroneous       |     |

|          | program a warning is generated of the use of portB as output port          |     |

|          | without corresponding trisb setting at location 3Fh. (b)in the correct     |     |

|          | program the rule is validated as the antecedent and its consequent         |     |

|          | are satisfied at locations 3Eh and 3Bh respectively.                       |     |

Fig. 4.5 The directed graph representations for the delay routines given in 117 Table 4.7 where each node numbered in bold represents an instruction and arrows represent the control flow between instructions. (a) shows the digraph for the correct version and (b) shows the same for the incorrect version.

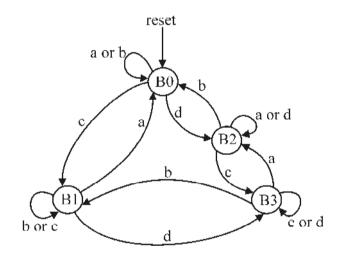

| Fig. 5.1 | State transition diagram showing the bank switching scheme.                                                     | 130 |

|----------|-----------------------------------------------------------------------------------------------------------------|-----|

| Fig. 5.2 | Flowchart explains the identification and pruning of redundant MBSWC in the machine code sequence of a program. | 133 |

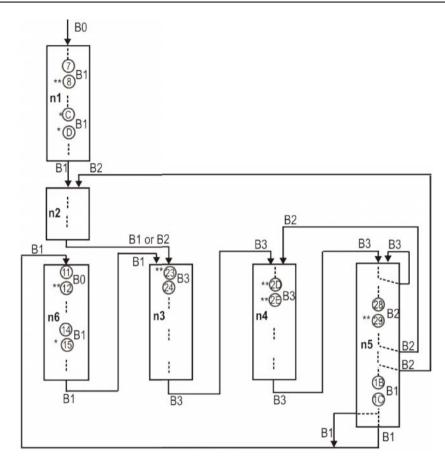

| Fig. 5.3 | CFG of the sample program for the analysis.                                                                     | 137 |

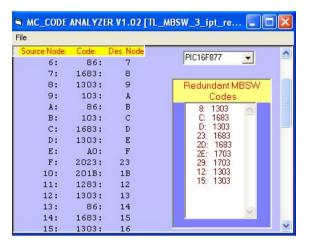

| Fig. 5.4 | Screen shot of the developed MC_CODE ANALYZER v1.02 for the sample program.                                     | 138 |

| Fig 5.5  | Screen shot of the developed MC_CODE ANALYZER v3.00 for the sample program.                                     | 138 |

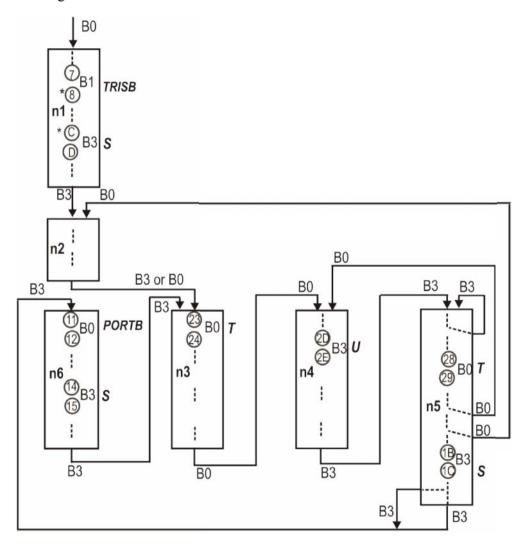

| Fig. 5.6 | CFG of the sample program with the worst case data allocation scheme.                                           | 145 |

| Fig 5.7  | The number of redundant bank switching instructions reported in the 64 data allocation schemes of the program.  | 147 |

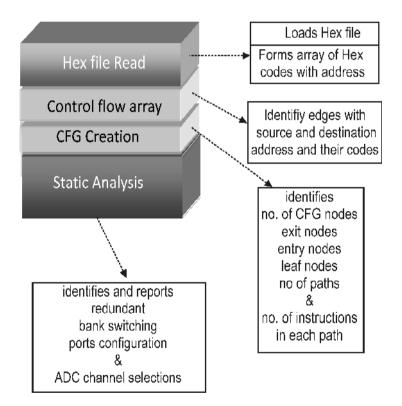

Fig. 5.8 Various steps realized in software for the code optimization. 149

# **ABBREVIATIONS**

| ADC    | : | Analog to Digital Converter                    |

|--------|---|------------------------------------------------|

| AMB    | : | Active Memory Bank                             |

| ASIC   | : | Application Specific Integrated Circuit        |

| BDM    | : | Background Debug Mode                          |

| CASE   | : | Computer Aided Software Engineering            |

| CFC    | : | Control Flow Checking                          |

| CFE    | : | Control Flow Errors                            |

| CFG    | : | Control Flow Graph                             |

| CISC   | : | Complex Instruction Set Computer               |

| CPU    | : | Central Processing Unit                        |

| DSP    | : | Digital Signal Processor                       |

| EEPROM |   | : Electrically Erasable Programmable Read Only |

| Memory |   |                                                |

| FPGA   | : | Field Programmable Gate Array                  |

| ICE    | : | In-Circuit Emulators                           |

| IDE    | : | Integrated Development Environment             |

| IPO    | : | Interprocedural Optimization                   |

| JTAG   | : | Joint Test Action Group                        |

| MBSD   | : | Model-Based Software Debugging                 |

| MCU    | : | Microcontroller Unit                           |

| NVP    | : | N-version programming                          |

| OCD    | : | On-Chip Debuggers                              |

| OCG    | : | Omniscient Code Generation                     |

| PAMB   | : | Previously Activated Memory Bank               |

| PDG    | : | Program Dependence Graph                       |

| PELAS  | : | Program Error–Locating Assistant System        |

| PGO    | : | Profile-Guided Optimizations                   |

| PSoC  | : | Programmable System on Chip                   |

|-------|---|-----------------------------------------------|

| RAM   | : | Random Access Memory                          |

| RB    | : | Recovery Blocks                               |

| RISC  | : | Reduced Instruction Set Computers             |

| ROM   | : | Read Only Memory                              |

| RTOS  | : | Real Time Operating System                    |

| SDG   | : | System Dependence Graph                       |

| SFR   | : | Special Function Register                     |

| SIHFD | : | Software Implemented Hardware Fault Detection |

| SIMD  | : | Singe Instruction Multiple Data               |

| SIS   | : | Signatured Instruction Streams                |

| SoC   | : | System on Chip                                |

| STAD  | : | System for Testing and Debugging              |

| VHDL  | : | VHSIC Hardware Description Language           |

| VHSIC | : | Very High Speed Integrated Circuit            |

| VLIW  | : | Very Large Instruction Word                   |

| VSA   | : | Value-Set Analysis                            |

| WET   | : | Whole Execution Trace                         |

# **1** INTRODUCTION

| Ň              | 1.1 Background and Motivation              | 2   |

|----------------|--------------------------------------------|-----|

|                | <ul> <li>Reliable Software</li> </ul>      |     |

|                | <ul> <li>Redundant Codes</li> </ul>        |     |

|                | <ul> <li>Software Constraints</li> </ul>   |     |

| :              | 1.2 Embedded System Development            | 6   |

|                | Real Time Systems                          |     |

|                | 1.3 Validation and Optimization Techniques | .10 |

| X              | 1.4 Programmable System on Chip (PSoC)     | .12 |

| $(\mathbb{N})$ | 1.5 Thesis Roadmap                         | .13 |

| $\cup$         | 1.6 Summary                                | 15  |

These days embedded systems are everywhere, appearing in places like the home, office, industry, transport, communication, automobile, robotics and in safety-critical applications such as military, medical and nuclear systems where human lives are at stake [1, 2, 3]. An embedded system can be defined as: *A system whose principal function is not computational, but has embedded software and computer hardware, which makes it a system dedicated for an application(s) or specific part of an application or product or part of a larger system [4, 5]. It is often a complex mix of external stimuli and system responses, controlled by one or more processors and dedicated hardware [6].*

Testing and debugging of embedded software remains a black art, with only ad hoc methods and techniques available. Tool availability dictates the quality of a testing process. The implications of software failure are much more severe in

#### Chapter 1

embedded systems than in desktop systems [6]. The lockout of a PC for sometime may result in loss of certain files or results of some application program, whereas suspending a time critical task controlled by an embedded system could be disastrous. Embedded systems are dedicated to specific tasks which means that design engineers can optimize it for high performance and reliability because the range of tasks the device must perform is well bounded. Due to strict timing constraints owing to real time concerns, the code optimization problem is more complex than for general purpose systems. It is desirable to have automated debugging, code validation and optimization methods which utilize the vast power of host machines available today to generate efficient machine codes. An efficient compiler can provide compact code, without having to learn the intricacies of the device architecture. This makes these devices more accessible to engineers with limited programming experience who are increasingly using MCUs in their product designs [7, 8].

#### **1.1 Background and Motivation**

Most of today's technological application utilizes embedded processors as a part of their infrastructure. It is common to select a processor based on its performance and to rely on the compiler to deliver this performance. This is particularly true of high-performance RISC (Reduced Instruction Set computer) based devices. Often performance is found to be hindered by the constraints of available debugging technology [7]. Developing programs for these systems in assembly language will take more coding time, as it is less flexible, than in a higher-level language. But developers prefer assembly language modules for critical real time applications requiring stringent timing and code size. The reliability and short time-to-market requirements of embedded systems are much better met by using high level language compilers. Even though code optimization

Department of Computer Science

is integrated with some of the compilers, they cannot eliminate code redundancy in many cases. Typically, a developer would guess what the problem is and try to gain visibility on the suspect variables or code segments by adding debugging statements, assertions, and breakpoints into the program. This trial and error process can be time consuming for long running programs. Moreover, a developer's intuitions may not necessarily be dependable especially if the errors are caused by his own misconceptions in the first place. [9].

#### **1.1.1 Reliable Software**

The development of error-free software for complex real time systems is an achievable goal within the reach of current software development technology. There are various approaches for developing highly dependable software through software fault tolerance techniques that uses diversity as the main ingredient [10, 11]. Static bug detection methods attempt to analyze a program for possible bugs without running it. Static tools can verify that a program is correct for all inputs, whereas dynamic tools can only find errors triggered by input test cases [9]. The notion of static program slicing was first proposed by Mark Weiser as a debugging aid [12]. In-lining of assembly code in high level language is a characteristic for embedded system software development to enable direct access to the device's hardware. Static analysis on machine code rather than source code eliminates the requirement of knowledge of the semantics of high level language. Several techniques have proposed to obtain information from executables by means of static analysis [13, 14, 15]. In the existing static bug detection methods, program verification is indecisive in general, and has only been applied successfully to small programs. Furthermore, static tools often require manual specification. Though dynamic program slicing is useful in debugging programs, the size of dynamicdependence graphs can be very large and thus it is not possible to keep them in

Cochin University of Science and Technology

memory for realistic program runs [16]. All these techniques for developing dependable software cause software overheads to the system.

#### **1.1.2 Redundant Codes**

Most of the embedded control systems are designed around a microcontroller unit which integrates on-chip program memory for storing and executing application code, data memory (RAM), various peripherals and I/O ports. Due to their architectural features there are various possibilities of introducing redundant codes by the programmer/compiler. The integration of processor cores and memory in the same chip effects a reduction in the chip count. leading to cost effective solutions. Typical examples of optional memory modules integrated with the processor on the same chip are: Instruction Cache, Data Cache, and on-chip SRAM. Many MCUs have banked memories that cannot be addressed simultaneously. Bank switching is a technique that increases the program and data memory in microcontrollers without extending the address buses [17]. A banksensitive program statement requires the appropriate bank to be made active prior to its execution. Use of macros simplifies the program development by managing memory resources of the target processors [18]. But, when they are used without care there is a possibility of introducing unnecessary bank select instructions which make the program too large for the device's program memory. Advanced compilers are utilizing algorithms for optimization technique to minimize the overhead of bank switching, but do not guarantee the optimal placement of bank selection instructions [17]. Generating efficient memory access code for bank switched architectures is still a challenging research problem. I/O port direction switching too may cause redundancy.

Department of Computer Science

# **1.1.3 Software Constraints**

The increasing complexity of embedded systems and the increasing need for development standards in building safety-critical systems are driving development groups to use more systematic processes [19]. In embedded applications, the cost and the short time-to-market are the leading issues [20]. It is highly desirable to develop an easy method, which will take the burden away from the software engineer by automating the error detection, identification and location steps [21] resulting in improved quality while shortening design cycles [22]. Embedded software must meet conflicting requirements such as being developed rapidly, running on resource-constrained platforms and being highly reliable. Static program analysis can help meet all of these goals [23]. Static analysis is important as these systems are used in safety critical applications and can be hard to upgrade once deployed; it is useful to detect software bugs early [6, 24, 25]. Some of the techniques proposed to find bugs in software automatically [26, 27, 28] require sophisticated program analysis. In this context a software tool to assist programmers to develop the application programs for the embedded controllers in assembly language as well as in high level language with more efficiency would be of great use.

The present state-of-the-art technology in system development uses tools like in circuit debuggers and loaders so that the compiled code can be transferred to the system and tested in real time. The integration of a code validation and optimization tool will easily fit into such a development environment for error free and efficient program development. To the best of author's knowledge, the related literature is limited to a method for statically guaranteeing stack safety of interrupt-driven embedded software based on context-sensitive dataflow analysis of object code [24], model checking of microcontroller assembly programs [29], static

Cochin University of Science and Technology

analysis on embedded assembly code to validate DSP software [30] and code optimization [17, 31, 32, 33, 34].

# **1.2 Embedded System Development**

Embedded systems require specialized tools and methods to be efficiently designed. The various phases in a design cycle include system specification and design, hardware/software design and debug, prototype debug and system test. The specific toolset necessary depends on the nature of the project to a certain extent. At a minimum, a good cross compiler and good debugging support are needed. In many situations, facilities such as in-circuit emulators (ICE), simulators, and so on are needed. The traits that separate embedded software from applications software are [6]:

- Embedded software must run reliably without crashing for long periods of time.

- Embedded software is often used in applications in which human lives are at stake.

- Embedded systems are often so cost-sensitive that the software has little or no margin for inefficiencies of any kind.

- Embedded software must often compensate for problems with the embedded hardware.

- Real-world events are usually asynchronous and nondeterministic, making simulation tests difficult and unreliable.

- A company can be sued if their code fails.

The possible stages in the development process for the program of a simple embedded system project are similar to those of a desktop/personal computer. The programmer writes the program, called the source code, in high level/assembler 6 Department of Computer Science

#### Chapter 1

necessary to write a program in Assembler, assemble it, simulate it and then download it to a target system using a programmer. The latter must be built or bought, or designed in to the target system. With certain IDEs like MPLAB, software tools can be bought and then integrated, both from Microchip and from other suppliers. This includes alternatives to what MPLAB already offers – e.g. Assemblers or simulators, as well as tools which offer much greater development power, like C compilers or emulator drivers.

In times past, the process of downloading the program to a microcontroller always used to require the IC carrying the memory (whether a stand-alone device or memory in a microcontroller) to be placed in a programmer. This was linked to a desktop computer for the process to be carried out. As memory technology has improved, it has become increasingly easy to design the necessary programming circuitry into the target system. This means that many microcontrollers can now be programmed in situ, i.e. within the target system. Most of the modern microcontrollers are equipped with on-chip program memory using Flash technology.

If a systematic approach to test and realization is followed the first step is to ensure the correct power supply, proper running of oscillator, correct status of the Reset pin and a properly downloaded program. Once these fundamental conditions have been satisfied, a further set applies if the system is to run continuously and achieve a moderate level of functionality. These include plausible circuit and program designs, correct hardware assembly and all the peripherals being configured appropriate to the situation. As the conditions indicated are met, the system should progress to a stage of optimization. Now it shows a good level of functionality, although still imperfect in some areas. From here it is likely that further tests must be accompanied by ongoing incremental design development, which may lie in either hardware or the program. Finally, one expects to see a system functioning to the full anticipated level of performance [35].

In this procedure our work contributes to the early validation and optimization of embedded software by conducting a static analysis on the machine code. This takes care of any error in the instruction sequence including the testing of configuration of peripherals to see that it is appropriate to the situation resulting in some sort of validation and optimization as well as the elimination of redundant instructions.

#### **1.2.1 Real Time Systems**

A system is said to be *real-time* if the total correctness of an operation depends not only upon its logical correctness, but also upon the time in which it is performed. Many embedded system must meet *real-time constraints*. A real-time system must react to stimuli from the controlled object (or the operator) within the time interval dictated by the environment. A hard real-time system guarantees that critical tasks complete on time. The application may be considered to have failed if it does not complete its function within the allotted time span. Examples of hard real-time systems include components of pacemakers, anti-lock brakes and aircraft control systems. In firm real-time systems infrequent deadline misses are tolerable, but may degrade the system's quality of service. The usefulness of a result is zero after its deadline. In soft real-time systems violation of constraints results in degraded quality, but the system can continue to operate. If the task should take, for example, 4.5ms but takes, on average, 6.3ms, then perhaps the inkjet printer will print two pages per minute instead of the design goal of three pages per minute [6, 36].

Cochin University of Science and Technology

# **1.3 Validation and Optimization Techniques**

The most crucial step in embedded system design is the integration of hardware and software [7]. Software validation involves many activities that take place throughout the lifecycle of software development. A substantial portion of the validation process is software testing, which is the development of test procedures and the generation and execution of test cases. Validation confirms that the architecture is correct and the system is performing optimally. Target level testing occurs extremely late in the development lifecycle and only a small window is allocated for hardware/software integration testing [37]. The most difficult errors to reveal and locate are found extremely late in the testing process, making them even more costly to repair.

System integration requires special tools to manage the complexity: tools that (mostly) reside on the development platform but that allow the programmer to debug a program running on the target system [6]. At a minimum these tools must:

- Include a debug kernel for controlling the processor during code development

- Support a convenient means to replace the code image on the target

- Provide non-intrusive, real-time monitoring of execution on the target.

The process of integrating embedded software and hardware is an exercise in debugging [6]. The integration phase really has three dimensions to it: Hardware, software, and real-time. The hardware can operate as designed, the software can run as written and debugged, but the product as a whole can still fail because of real-time issues. Emulators are the premier tools for HW/SW integration. An emulator's close coupling of run control, memory substitution, and trace facilities generates a synergism that significantly increases the power of each component.

Introduction

Optimization is very important for embedded systems, due to limited system-on-a-chip memory sizes, real-time constraints of embedded applications, and the need to minimize power consumption of mobile devices [38]. The compilation process starts with source code analysis and source level optimization. Standard optimizations techniques, such as constant folding, common subexpression elimination, or jump optimization [39, 40] need only a minimum of machine-specific information. These are also performed at the intermediate representation (IR) level, where complex source code constructs have already been split into a simple form, such as three-address code. In case of multimedia applications mapped to VLIW processors, loop unrolling, where loop iterations are duplicated, resulting in larger basic blocks and thereby in a higher potential for parallelization of instructions during scheduling, is a very effective means of code optimization [38]. Function inlining is a well-known technique, in which function calls are replaced by copies of function bodies, so as to reduce the calling overhead. These optimizations come at the price of an increased code size. When the machine independent IR statements are mapped to assembly instructions, all machinespecific features, such as special-purpose registers, complex instruction patterns, and inter-instruction constraints need to be taken into account. This is what makes efficient code generation for embedded processors generally difficult.

More advanced approaches use a dedicated optimization phase for partitioning the program variables between the dual memory banks which are accessible in parallel in such a way, that potential parallelism is maximized [41, 42]. In embedded processors having partitioned memory architecture, where the memory banks cannot be accessed in parallel minimal placement of bank switching instructions results in code optimization [17, 31, 32, 33, 34]. Post pass optimizers usually work on the assembly language or machine code level which takes the executable output by an "optimizing" compiler and optimize it even further. For

Cochin University of Science and Technology

embedded systems high code quality is much more important than high compilation speed.

Debugging software is an inevitable and arduous task. The responsibility of the fault diagnosing is to delve deeply into the bug and determine the root cause of the malfunction. Embedded systems provide the additional challenges of limited visibility of the system through a small number of inputs and outputs. Today's debugging methodologies for embedded systems can be inadequate for overcoming this problem with a low cost and flexible solution. The capability of automatic detection, identification and location of an extensible set of logic errors adds intelligence to the debugger [21, 43].

#### **1.4 Programmable System on Chip (PSoC)**

FPGA (Field Programmable Gate Array) and ASICs (Application Specific Integrated Circuits) are the modern revolutions in embedded-systems design since processors and associated peripherals can be integrated to a single chip [44, 45, 46]. ASICs are also the technology of the SoC (System on Chip) revolution that is still being sorted out today. Until recently, designers have been limited to the choice of microprocessor versus microcontroller. Now, at least for mass-market products, it might make sense to consider a system-on-a-chip (SOC) implementation, either using a standard part or using a semi-custom design compiled from licensed intellectual property. Today, it's common for a customer to completely design an application-specific embedded system containing multiple CPU elements and multiple peripheral devices on a single silicon die. Individual elements are designed in the form of "synthesizable" VHSIC (very high speed integrated circuit) Hardware Description Language (VHDL) or Verilog codes [44, 46]. Engineers connect these modules with custom interconnect logic, creating a chip that contains the entire design. Unlike an ASIC, an FPGA can be reprogrammed without a high silicon development charge.

## **1.5 Thesis Roadmap**

This Thesis deals with the constraints in the existing tools in embedded software development and some solutions. A code validation, fault localization and optimization tool and its applications in RISC (Reduced Instruction Set Computer) microcontrollers, to assist in efficient software development is described. This is achieved through the static analysis of machine codes by applying the rules and algorithms formulated. An algorithm which helps to eliminate the redundant bank switching instructions in partitioned memory architectures is also presented.

The thesis explores the various debugging and optimization technologies available for embedded systems in chapter two. The static and dynamic analysis techniques for localizing errors in a program are discussed. Static analysis of executables, various program slicing methods and their usefulness in debugging are examined. The role of simulation in providing a useful environment for software testing is considered. The scope of oscilloscopes and logic analyzers in debugging embedded software are limited due to the inaccessibility of buses of microcontrollers. In Circuit Emulators as a powerful technique for testing both hardware and software are examined. On chip debug supports like BDM (Background Debug Mode) and JTAG (Joint Test Action Group) standard interface protocols are briefed. Verification and Validation- the two important components of integrating hardware and software are explained. Fault tolerance through control flow checking for dependable embedded system development and various optimization techniques provided by advanced compilers are also discussed.

Chapter three introduces the methodology adopted by the static machine code analyzer for the architecture oriented validation, fault localization and optimization of embedded software. The concepts behind the program partitioning and formation as well as codification of rules are briefed. Analysis of machine code resulting in validation and optimization is presented. Programming in Visual Basic and development support systems are discussed.

Chapter four describes an approach towards code validation of RISC microcontrollers, at the level of machine instruction stream. Formulation and codification of rules governing the occurrence of illegal instructions and code sequences for executing the CPU/Integrated peripheral functions is explained. Development of a prototype based on PIC 16F87X microcontrollers is discussed. Retrieval of machine code from *Intel hex* file and the construction of CFG (Control Flow Graph) from the machine code array are described. Identification of all possible execution paths in the CFG leading to the analysis of the machine code by applying the rules governing the occurrence of illegal instruction sequence is discussed. The process of locating, diagnosing and reporting of errors and possible error corrections are presented. Results of the analysis are discussed.

Chapter five deals with the optimization of embedded code by the elimination of redundant bank switching instructions in application programs for microcontrollers with banked memory architecture. A state transition diagram representing the memory bank switching corresponding to each bank selection instruction is drawn and a relation matrix, for the active memory bank state transition, is derived. The algorithm developed for eliminating the redundant bank switching instructions using the relation matrix and its implementation in Visual Basic is explained. Analysis of the machine code to take care of the intraprocedural, loops and interprocedural routines of an application program is also shown. A compiler strategy that can automatically determine the optimum data allocation among the memory banks resulting in the minimum bank switching code is presented. Elimination of redundant codes based on some of the rules stipulated in chapter four are also considered.

Chapter six is to enumerate the conclusions of this research work. The advantages and disadvantages of static analysis on machine code for the validation and optimization of embedded system code are listed. The extension of the use of these techniques to other applications is suggested. The major contributions of this research work as well as suggestions for improving the performance of the techniques are described.

## **1.6 Summary**

This thesis proposes a static analyzer for embedded system software, which is close to a target level testing tool that is portable. Primary goal is to develop techniques that can be implemented in tools that are useful for people developing embedded software for the early validation and optimization of embedded software by conducting a static analysis on the machine code. The focus of our work is to develop methods that automatically localize faults and thus enhance the debugging process as well as reduce human interaction time without software or runtime overhead. Analysis is done on machine code rather than source code because this eliminates the requirement of knowledge of the semantics of high level language/assembly language and it is independent of the compiler; developers are free to change compilers or compiler versions.

Cochin University of Science and Technology

2

# **REVIEW OF DEBUGGING AND OPTIMIZATION TECHNOLOGIES**

|                                  | 2.1 Embedded System Constraints                                 | 18 |

|----------------------------------|-----------------------------------------------------------------|----|

|                                  | 2.2 Software Development Tools                                  | 21 |

| $\left[ \left\{ \right. \right]$ | <ul> <li>Embedded Software</li> </ul>                           |    |

|                                  | <ul> <li>Fault Localization Techniques</li> </ul>               |    |

|                                  | <ul> <li>Debugging Systems and Tools</li> </ul>                 |    |

|                                  | 2.3 Hardware and Software Integration                           | 56 |

|                                  | 2.4 Control Flow Checking                                       |    |

|                                  | 2.5 Optimization                                                |    |

|                                  | <ul> <li>General Optimizations</li> </ul>                       |    |

| ĸ                                | <ul> <li>Processor Specific Optimizations</li> </ul>            |    |

| Ř                                | <ul> <li>Interprocedural Optimizations</li> </ul>               |    |

| $\mathbb{C}^{-1}$                | <ul> <li>Profile-Guided Optimizations</li> </ul>                |    |

|                                  | <ul> <li>Optimization of Bank Switching Instructions</li> </ul> |    |

|                                  | 2.6 Summary                                                     | 69 |

|                                  |                                                                 |    |

Embedded applications are among the most complex software systems being developed today. Embedded systems control many of the common devices in use today. Since the embedded system is dedicated to specific tasks [38], design engineers can optimize it, reducing the size and cost of the product, or increasing the reliability and performance. Embedded applications have traditionally been event driven rather than computation dependent; viz not used for general purpose computing applications. Consequently, software development of embedded systems has become a very challenging and critical task. The state-of-the-art is to

be incorporated with new and innovative technologies to ensure that the customer requirements are met quickly and cost effectively.

Superficially, there are great similarities between the way embedded systems are programmed and how desktop software is developed. For example, much the same programming languages - C and C++ - are the most common. The attitude toward bugs is where the approaches differ [47]. Desktop software is commonly shipped with known bugs. These may be limitations in functionality or degradations in performance over time, for example. This is considered acceptable, as failure of the software is unlikely to cause any significant harm - certainly not to put life in danger. The worst case generally results in loss of data. The attitude toward bugs in embedded software differs in three key respects:

- Many embedded applications are concerned with machinery, the malfunction of which, would be dangerous and/or expensive

- Issuing software updates for embedded applications is rarely convenient or economic

- An embedded system may be run for long periods without being reset or power-cycled. So bugs that accumulate in significance over protracted execution times are more likely to become critical.

### 2.1 Embedded System Constraints

General purpose microprocessors do not contain RAM, ROM or I/O ports as such. But a microcontroller has CPU, ROM, RAM, I/O ports, timer, ADC and other peripherals integrated. Fig. 2.1(a) and (b) shows the details. A typical embedded system contains a single chip microcontroller and is programmed for a pre-defined, dedicated task. The logic is often invisible as it forms part of the appliance or system.

and inbuilt resources also being restricted. Although the amount of memory may not be small, it typically cannot be added on demand [7]. The current methods and tools for software testing and debugging require computing resources that are not available on the target environment. Target hardware of an embedded system normally will not support software development tools. Usually the application program is developed on a host platform and cross compilers and linkers are used to generate code and download it to the target processor by the help of loaders. Therefore, a large gap exists between the methods and tools used during evaluation on the host and those used on the target. Tools that run on the host provide a high level interface and give users detailed information on and control over their program execution. However, little is provided on the target. Typically, the best information obtainable is a low-level execution trace provided by an in-circuit emulator. Unfortunately, many errors are only revealed during testing in the target environment. The software must not only be correct, but must also interface properly with the devices it is controlling.

Embedded software is often constrained by

- Real-time constraints

- Embedded target environments

- Distributed hardware architectures

- Device control dependencies

Each of these properties of embedded software severely restricts execution visibility and control, which consequently restricts the testing and debugging process [37]. The current ability of designers to determine the reliability of embedded system depends on the techniques used in the specification, design and implementation of embedded software [2].

Nowadays, resorting to assembly language is rarely a convenient option. The complexity of the software, short development time and reliability requirements force the use of high level language for program development, while the critical modules are developed in assembly language. A thorough understanding of the efficient use of high level language and the effects and limitations of optimization are crucial. Otherwise, memory demand and real-time overheads do build up and would become apparent only late in a project, when a redesign of the software is not an option [7].

Consumer applications are characterized by tight time-to-market constraints and extreme cost sensitivity. This leads to some interesting challenges in software development. Currently most of the consumer products support upgradable software. If some bug is detected after the deployment of a product, a new version of the software can be reloaded into the device. But in safety critical systems such upgrading might be impractical.

## 2.2 Software Development Tools

To develop even a simple project, a selection of different software tools is beneficial. These are usually bundled together into what is called an Integrated Development Environment [35]. The development of error-free software for complex real- time systems, such as highly critical systems in defense, atomic power plants, air traffic control or space craft, is an achievable goal within the reach of current embedded software development technology. The software development technique includes process definition, state-of-the-art software engineering principles, rigorous inspection of work products across the process, independent software verification, sophisticated defect cause analysis and use of specialized tools to enhance development and testing. To meet the increased need

for software of the highest quality, knowledge engineering, expert systems, and value gained from "lessons learned" can be applied [48].

As processor architecture evolves and the complexity of instructions increases, the role of the compiler in application development becomes increasingly important. The applications developed in the embedded industry are becoming progressively more intricate, placing even more emphasis on software tools. An optimal compiler can not only increase the performance of an application, but can also decrease development cost and engineering cycle time, thereby accelerating time to market (TTM) [49]. With modern simulation technology, the code can be run, together with any real-time operating system on the host computer, and link it to a graphical representation of the user interface (UI). This enables developers to interact with the software as if they were holding the device in their hand. This capability makes checking out all the subtle UI interactions a breeze [7]. Code development techniques can be automated improving quality while shortening design cycles. With the spread of desktop computers, the mid-1980s have seen the introduction of automated environments and tools that make it practical and economical to use formal system-development methods. This technology known as CASE (Computer Aided Software Engineering), lets computer professionals develop and validate system designs and specifications, automating and enhancing the manual methods of the 1970s and 1980s [50]. CASE tools, which impose a systematic approach on program writing, grow ever more popular as adjuncts to assemblers and compilers. CASE tools enforce documenting and modeling an application from the initial user requirements through design and implementation, and can test for consistency, completeness, and conformance to standards. They help in simulating, organizing, documenting, and generating specifications for the application. They provide facilities for drawing and managing system architectural diagrams, describing and defining functional and data objects,

Department of Computer Science

identifying relationships between system parts, and providing annotations to aid project management [51]. A Source-level Debugger together with an optimizing compiler provides a fully integrated real-time software development environment for embedded applications that encompasses source-level debugging, windoworiented editing, automated program building, execution profiling, and project/version control.

Right choice of the software development tools enables the programmers to develop more reliable, more capable, higher performance software in less time, at a lower development cost. Tools for embedded system development include: cross compilation systems, in-circuit tools, simulators, debuggers etc. The features, benefits and tradeoffs of these tools, and how they apply to each stage of software development, are examined.

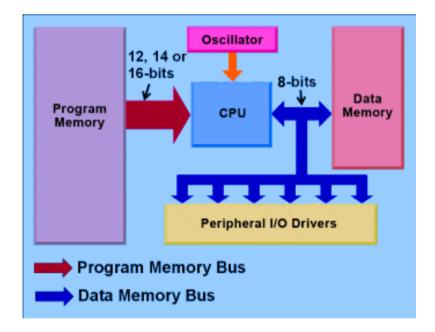

#### 2.2.1 Embedded Software

NASA, in their report [25] defines Embedded Software as software that is designed to execute in a computational device in order to control or to perform a specific process in support of an end item. The activities that involve testing, debugging, verification and validation in a typical software development process [52] are shown in Fig. 2.2. The starting point of system software development is requirement analysis and design. This is followed by implementation which involves developing code for all units and testing them individually. The final stage is integration and software component level testing [53]. An embedded system software development environment is an integrated collection of software development tools that manage the entire embedded software development process. Some of the technical and management activities included in independent verification and validation for embedded software are: requirements analysis and tracing; peer reviews, status monitoring and reporting, walk-through, dynamic