# DESIGN TECHNIQUES FOR SIGMA-DELTA BASED ADC FOR WIRELESS APPLICATIONS

A thesis submitted by

#### **BABITA ROSLIND JOSE**

for the award of the degree of

#### **DOCTOR OF PHILOSOPHY**

(Faculty of Engineering)

JANUARY 2010

# DESIGN TECHNIQUES FOR SIGMA-DELTA BASED ADC FOR WIRELESS APPLICATIONS

A thesis submitted by

#### **BABITA ROSLIND JOSE**

for the award of the degree of

#### DOCTOR OF PHILOSOPHY

(Faculty of Engineering)

Under the guidance of

Dr. P. MYTHILI

DIVISION OF ELECTRONICS

SCHOOL OF ENGINEERING

COCHIN UNIVERSITY OF SCIENCE AND TECHNOLOGY

KOCHI – 682 022

JANUARY 2010

#### **DECLARATION**

I hereby declare that the work presented in this thesis entitled "DESIGN TECHNIQUES FOR SIGMA-DELTA BASED ADC FOR WIRELESS APPLICATIONS" is based on the original research work carried out by me under the supervision and guidance of Dr. P. Mythili, Reader, Division of Electronics, School of Engineering, Cochin University of Science and Technology, Kochi-22. This work did not form part of any dissertation submitted for the award of any degree, diploma or other similar title or recognition from this or any other institution.

Kochi – 682 022 30<sup>th</sup> December 2009 **BABITA ROSLIND JOSE**

## Acknowledgements

I would like to express my gratitude to Dr. P. Mythili, Reader, Cochin University of Science and Technology, for the professional and personal guidance and the constant support at all stages of this research.

Also, I would like to thank Dr. Gopikakumari, Head of the department, for her constructive comments in Ph.D reviews

It is difficult to identify many friends who contributed so much unmentioned support. However, I am indebted to Shahana T. K, and Rekha K James for the wholehearted and enthusiastic help at all stages of this research. I take this opportunity to thank all the people in the department for their support.

Finally, I would like to thank our principal and office staff for all other logistical support.

Babita Roslind Jose

#### Abstract

Analog-to-digital Converters (ADC) have an important impact on the overall performance of signal processing systems. This research is to explore efficient techniques for the design of sigma-delta ADC, specifically for multi-standard wireless transceivers. In particular, the aim is to develop novel models and algorithms to address this problem and to implement software tools which are able to assist the designer's decisions in the system-level exploration phase. To this end, this thesis presents a framework of techniques to design sigma-delta analog-to-digital converters. We present different re-configurable sigma-delta modulator architectures, techniques for coefficient optimization and a tool box.

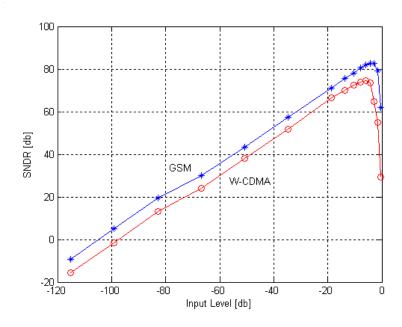

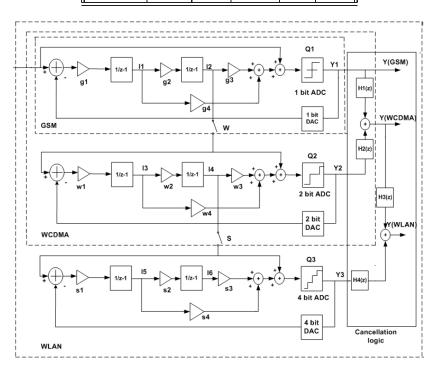

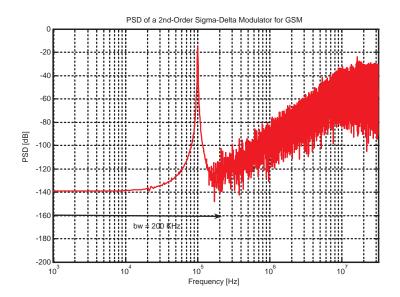

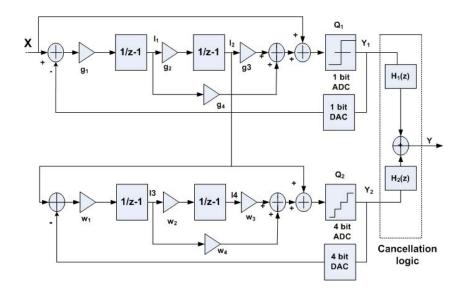

First, after introducing the basic concepts, a dual mode sigma-delta converter is presented. A modified cascaded 2-2 sigma-delta modulator topology is chosen to meet both Global System for Mobile communications (GSM) and Wideband Code Division Multiple Access (WCDMA) specifications. To reduce sensitivity to operational amplifier non-linearities, both stages are implemented using the sigma-delta modulator with feed forward signal path. Also presented is a cascaded 2-2-2 reconfigurable sigma-delta modulator that can handle GSM, WCDMA and WLAN standards. The modulator makes use of a low-distortion swing-suppression topology which is highly suitable for wide band applications. In GSM mode, only the first stage (2nd order sigma-delta ADC) is used to achieve a peak SNDR of 88dB with an over-sampling ratio of 160 for a bandwidth of 200KHz and for WCDMA mode, a 2-2 cascaded structure (4th order) is turned on with a 1-bit quantizer in the first stage and a 2-bit quantizer in the second stage to achieve 73 dB peak SNDR with an over-sampling ratio of 16 for a bandwidth of 2MHz. Moreover, a 2-2-2 cascaded MASH (Multistage noise shaped) architecture with 4-bit in the last stage is proposed to achieve a peak SNDR of 58dB for WLAN for a bandwidth of 20MHz. The novelty lies in the fact that unused blocks of second and third stages can be made inactive to achieve low power consumption. The configurable sigma-delta modulator has been designed in 0.18um CMOS technology, operating from 1.8V supply voltage. The proposed sigma-delta modulator for GSM/WCDMA/WLAN receiver was implemented as a fully-differential switched-capacitor (SC) circuit which has been simulated using SPICE. The design of the individual circuit blocks like operational transconductance amplifier (OTAs), switches, capacitors and comparators has been done based on behavioral simulation results. The modulator achieves a peak SNDR of 82/68/54 dB for GSM/WCDMA/WLAN standards respectively from the circuit-level implementation.

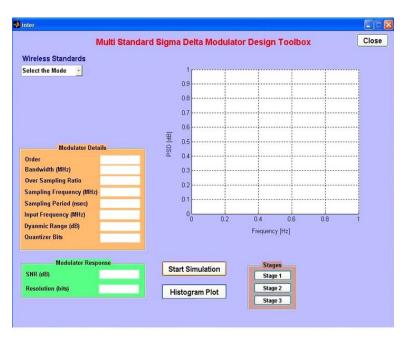

Secondly, to expedite the handling of complicated design calculations, a Graphical User Interface (GUI) based design tool is also proposed. In particular, multi-standard sigma-delta modulator design for three wireless communication standards consisting of GSM, WCDMA and WLAN is considered. A 2-2-2 reconfigurable sigma-delta modulator is chosen to meet the design specifications of the three standards. The toolbox incorporates most of the important sigma-delta non-idealities. The main non-idealities considered here are finite and nonlinear dc gain, slew rate and gain-bandwidth limitations, amplifier saturation voltage, capacitor mismatch, opamp input referred noise, kT/C noise, clock jitter and DAC capacitor mismatch. The sigma-delta modulator design tool is developed using the Graphical User Interface Development Environment (GUIDE) in Matlab $^{TM}$ .

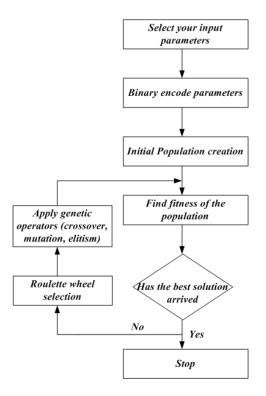

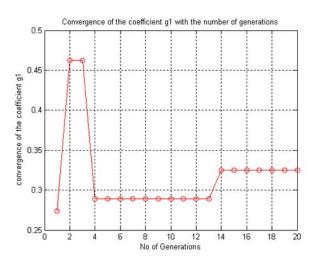

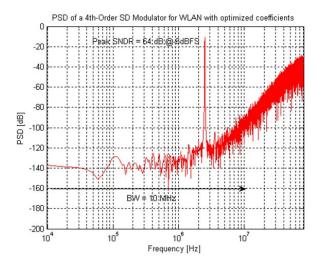

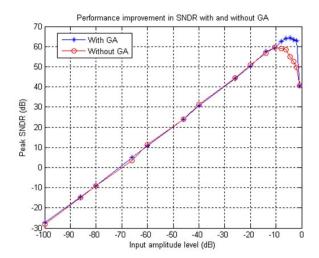

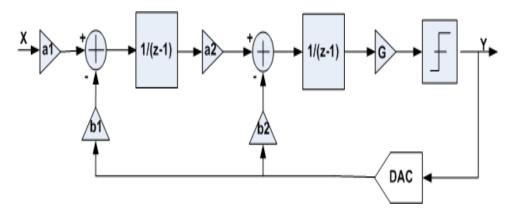

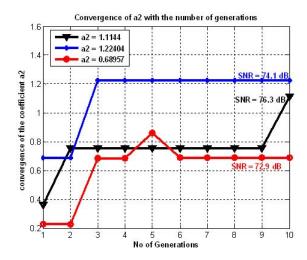

Finally, in sigma-delta modulator design, the scaling coefficients determine the peak signal-to-noise ratio. Therefore, selecting the optimum value of the coefficient is very important. Towards this, the design of a fourth-order multi-bit sigma-delta modulator suitable for Wireless Local Area Networks (WLAN) receivers with feed forward path is selected as an example. Further, a Genetic Algorithm (GA)-based search method is introduced. In particular, the proposed converter makes use of low-distortion swing suppression SDM (Sigma Delta Modulator) architecture which is highly suitable for low oversampling ratios to attain high linearity over a wide bandwidth. A second-order traditional topology has been chosen as the second design example to validate our proposed method. The basic aim is the identification of the best coefficients suitable for the proposed topology in order to achieve the desired signal-to-noise ratio. GA-based search engine is a stochastic search method which can find the optimum solution within a given set of constraints.

# Glossary

```

ASIC — Application Specific Integrated Circuit;

ADC — Analog-to-digital converter;

BW — Bandwidth;

CMOS —Complementary metal oxide semiconductor;

DAC — Digital to analog converter;

FPGA — Field Programmable Gate Array;

INL —integral non-linearity;

IFFT — Inverse Fast Fourier Transform;

GA — Genetic Algorithm;

GSM — Global System for Mobile communications;

GUI — Graphical User Interface;

GUIDE — Graphical User Interface Development Environment;

MASH — Multi-stage noise Shaped;

Opamp — operational amplifier;

OTA — Operational Transconductance Amplifier;

\Sigma \triangle— Sigma-delta;

SOC — System on Chip;

SC — Switched-capacitor;

SR — Slew rate:

SNDR — Signal to Noise-plus-Distortion Ratio;

SDM — Sigma Delta Modulator;

TSMC — Taiwan Semiconductor Manufacturing Company;

WLAN — Wireless Local Area Network;

WCDMA — Wideband Code Division Multiple Access;

WPAN — Wireless Personal Area Network;

UWB — Ultra Wide Band;

SDC — Sigma Delta Converter;

```

# Contents

| N | omer | ıclatur           | re                                              | $\mathbf{x}\mathbf{v}$ |

|---|------|-------------------|-------------------------------------------------|------------------------|

| 1 | Intr | $\mathbf{coduct}$ | ion                                             | 1                      |

|   | 1.1  | Motiv             | ation                                           | 1                      |

|   |      | 1.1.1             | Research Focus                                  | 3                      |

|   | 1.2  | Autho             | or's Contributions                              | 3                      |

|   |      | 1.2.1             | Other Contributions not Included in this Thesis | 6                      |

|   | 1.3  | Thesis            | S Outline                                       | 7                      |

| 2 | Bac  | kgroui            | $\operatorname{ad}$                             | 9                      |

|   | 2.1  | Radio             | Receiver Architectures                          | 11                     |

|   |      | 2.1.1             | Superheterodyne Receiver                        | 11                     |

|   |      | 2.1.2             | Direct Conversion Homodyne Receiver             | 12                     |

|   |      | 2.1.3             | Low-IF Receiver                                 | 12                     |

|   |      | 2.1.4             | Wideband IF Double-conversion Receiver          | 13                     |

|   | 2.2  | Analo             | g-to-digital Converters                         | 14                     |

|   | 2.3  |                   | fication of ADC                                 | 14                     |

|   |      | 2.3.1             | Nyquist rate ADCs                               | 15                     |

|   |      | 2.3.2             | Oversampling ADCs                               | 15                     |

|   | 2.4  | Basic             | Analog-to-Digital Conversion                    | 16                     |

|   |      | 2.4.1             | Sampling                                        | 17                     |

|   |      | 2.4.2             | Quantization                                    | 17                     |

|   |      | 2.4.3             | Quantization Noise                              | 20                     |

|   | 2.5  | _                 | ampling $\Sigma \triangle$ ADCs : Fundamentals  | 20                     |

|   |      | 2.5.1             | Oversampling                                    | 21                     |

|   |      | 2.0.1             | Oversampning                                    | 21                     |

|   |      | 2.5.2 Noise-shaping                                                                       |

|---|------|-------------------------------------------------------------------------------------------|

|   | 2.6  | $\Sigma \triangle$ Modulator                                                              |

|   | 2.7  | Performance Metrics for the $\Sigma \triangle$ ADC                                        |

|   | 2.8  | Traditional $\Sigma \triangle$ ADC Topology                                               |

|   |      | 2.8.1 Single-Loop Single-Bit $\Sigma \triangle$ modulators                                |

|   |      | 2.8.2 Single-loop Multi-bit $\Sigma \triangle$ Modulators                                 |

|   | 2.9  | Cascaded $\Sigma \triangle$ Modulators                                                    |

|   | 2.10 | Performance Comparison of Traditional $\Sigma \triangle$ Topologies 45                    |

|   | 2.11 | Chapter Summary                                                                           |

| 3 | Syst | sem Level Design and Analysis 47                                                          |

|   | 3.1  | Introduction                                                                              |

|   | 3.2  | Low-distortion Swing-suppression SDM                                                      |

|   | 3.3  | A Dual-mode $\Sigma\triangle$ Modulator Design $\ \ldots \ \ldots \ \ldots \ \ldots \ 49$ |

|   |      | 3.3.1 Estimation of Gain Coefficients                                                     |

|   |      | 3.3.2 Error cancellation                                                                  |

|   | 3.4  | Simulations                                                                               |

|   |      | 3.4.1 Integrator Output Swing                                                             |

|   |      | 3.4.2 Dynamic Range                                                                       |

|   | 3.5  | A Triple-mode $\Sigma\triangle$ Modulator Design                                          |

|   |      | 3.5.1 Modulator Architecture                                                              |

|   | 3.6  | Simulations                                                                               |

|   | 3.7  | Chapter Summary                                                                           |

| 4 | Circ | euit-level Design 66                                                                      |

|   | 4.1  | Introduction                                                                              |

|   | 4.2  | Sampled-Data vs. Continuous-Time                                                          |

|   | 4.3  | Switched-Capacitor Integrator                                                             |

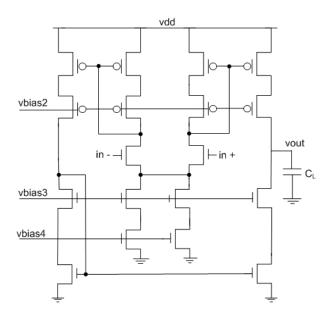

|   |      | 4.3.1 Operational Trans-conductance Amplifier (OTA) $$ 69                                 |

|   |      | 4.3.2 Common-mode Feedback                                                                |

|   |      | 4.3.3 Bias                                                                                |

|   |      | 4.3.4 Simulation Results of OTA                                                           |

|   |      | 4.3.5 Process Variation Analysis                                                          |

|   | 1.1  | Switches 78                                                                               |

|   | 4.5  | Circuit | t Noise                                           |

|---|------|---------|---------------------------------------------------|

|   | 4.6  | Sampli  | ing and Integrating Capacitors                    |

|   | 4.7  | Incom   | plete Linear Settling and Slew Rate Limitation 82 |

|   | 4.8  | Integra | ator Leakage and Amplifier Gain Requirements 83   |

|   | 4.9  | Quant   | izers                                             |

|   |      | 4.9.1   | Comparators                                       |

|   |      | 4.9.2   | Multi-bit A/D/A Converters                        |

|   |      | 4.9.3   | Digital-to-Analog Converters                      |

|   | 4.10 | Clocks  | 89                                                |

|   | 4.11 | Simula  | tion Results                                      |

|   | 4.12 | Layout  | Design                                            |

|   | 4.13 | Perform | mance Comparison                                  |

|   | 4.14 | Chapte  | er Summary                                        |

| 5 | Sign | na-delt | ta Modulator Design Tool 99                       |

|   | 5.1  | Motiva  | ation                                             |

|   | 5.2  | Introd  | uction                                            |

|   | 5.3  | Sigma-  | delta Modulator Design Toolbox                    |

|   | 5.4  | Sigma-  | delta Non-idealities                              |

|   |      | 5.4.1   | Clock Jitter                                      |

|   |      | 5.4.2   | Integrator Noise                                  |

|   |      | 5.4.3   | Switches Thermal Noise                            |

|   |      | 5.4.4   | Opamp Noise                                       |

|   | 5.5  | Integra | ator Non-Idealities                               |

|   |      | 5.5.1   | Gain Variations                                   |

|   | 5.6  | Operat  | tional-Amplifier Non-Idealities                   |

|   |      | 5.6.1   | Leak                                              |

|   |      | 5.6.2   | Finite and Non-linear dc Gain                     |

|   |      | 5.6.3   | BW and SR                                         |

|   |      | 5.6.4   | Saturation                                        |

|   | 5.7  | Circuit | t-related Non-idealities                          |

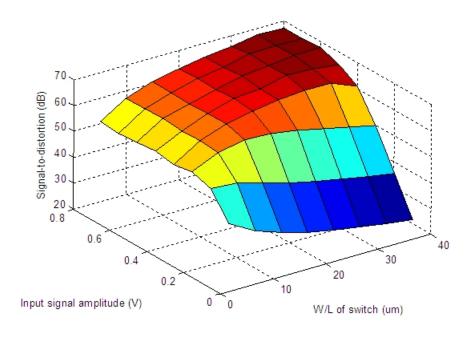

|   |      | 5.7.1   | Switch Non-linearity                              |

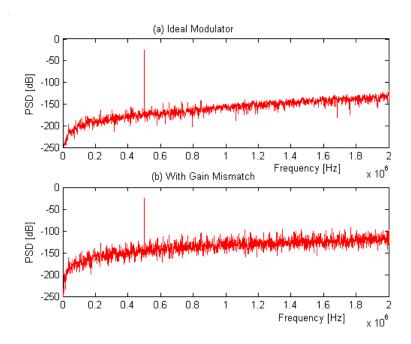

|   |      | 5.7.2   | Gain Mismatch                                     |

### CONTENTS

|                | 5.8   | DAC Non-linearity                             | 120 |

|----------------|-------|-----------------------------------------------|-----|

|                | 5.9   | Performance Analysis                          | 123 |

|                | 5.10  | Chapter Summary                               | 124 |

| 6              | GA-   | -based Optimization of Sigma-delta Modulators | 126 |

|                | 6.1   | Motivation                                    | 126 |

|                | 6.2   | Introduction                                  | 127 |

|                | 6.3   | Modulator Architecture                        | 127 |

|                | 6.4   | GA-Based Coefficient Optimization             | 131 |

|                |       | 6.4.1 Genetic Algorithm                       | 131 |

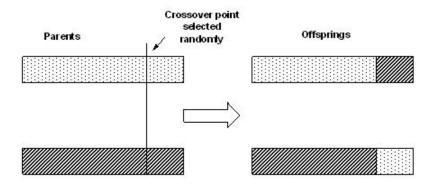

|                |       | 6.4.2 Using GA in $\Sigma\Delta$ ADC Design   | 133 |

|                | 6.5   | Simulation Results                            | 135 |

|                |       | 6.5.1 Case A                                  | 135 |

|                |       | 6.5.2 Case B                                  | 137 |

|                | 6.6   | Chapter Summary                               | 140 |

| 7              | Con   | aclusions and Future Work                     | 142 |

|                | 7.1   | Summary of the Thesis                         | 142 |

|                | 7.2   | Future Work                                   | 144 |

| $R_{\epsilon}$ | efere | nces                                          | 158 |

# List of Figures

| 2.1  | Ideal software radio transceiver                                                    | 10 |

|------|-------------------------------------------------------------------------------------|----|

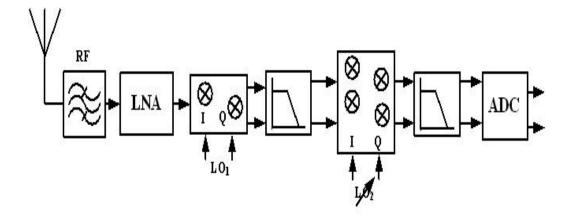

| 2.2  | Superheterodyne receiver                                                            | 11 |

| 2.3  | Direct conversion homodyne receiver                                                 | 12 |

| 2.4  | Low-IF receiver                                                                     | 13 |

| 2.5  | Wideband IF double conversion receiver                                              | 14 |

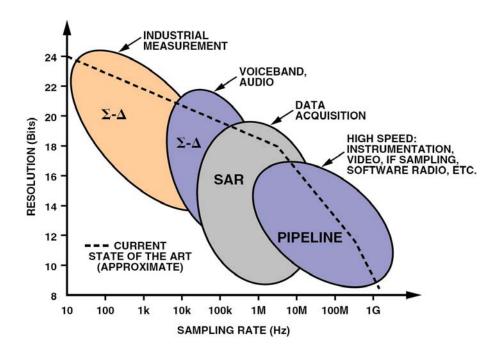

| 2.6  | Different ADC architectures, applications, resolution and sampling                  |    |

|      | rates                                                                               | 15 |

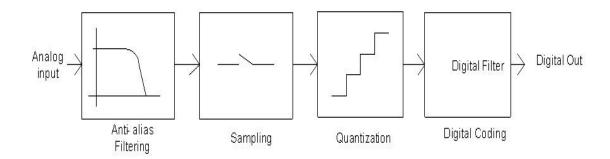

| 2.7  | Block diagram of analog-to-digital conversion                                       | 17 |

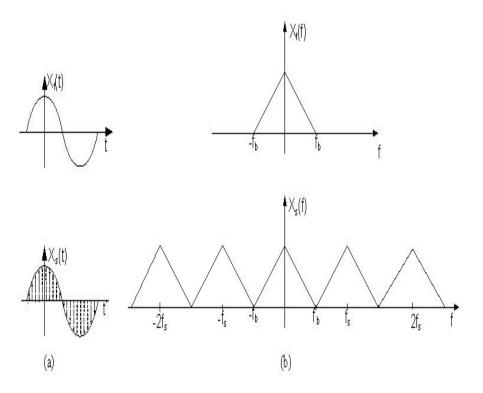

| 2.8  | Sampling operation (a) in time domain (b) in frequency domain .                     | 18 |

| 2.9  | (a) Characteristic transfer curve for multi-level quantization (b) Re-              |    |

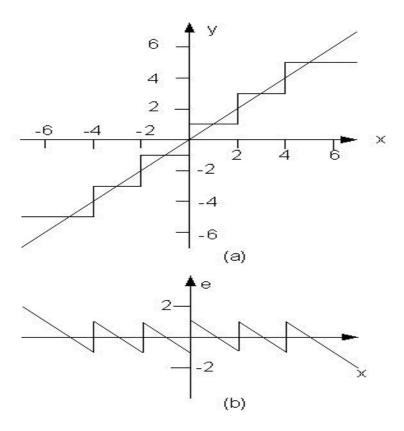

|      | sulting error                                                                       | 19 |

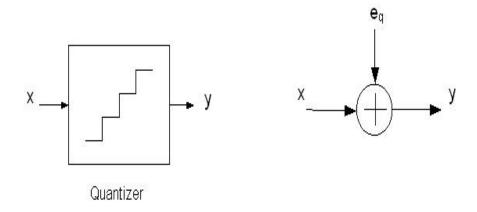

| 2.10 | Linear model of a quantizer                                                         | 20 |

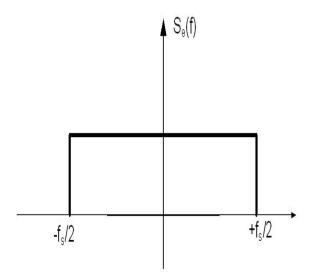

| 2.11 | Power spectral density of quantization noise                                        | 21 |

| 2.12 | PSD of the quantization error in an oversampled converter. Total                    |    |

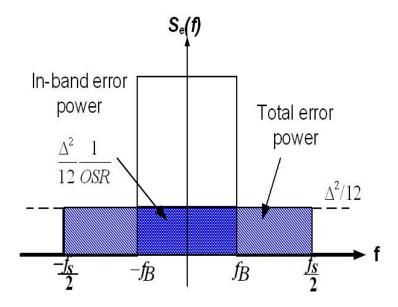

|      | power of the quantization error and power within the signal band                    |    |

|      | are highlighted                                                                     | 22 |

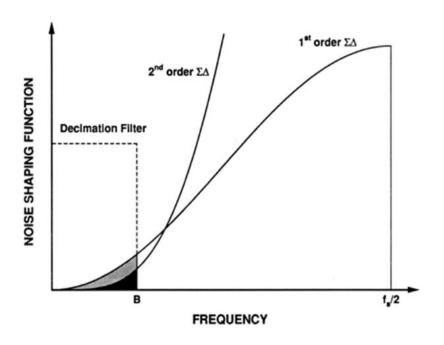

| 2.13 | Noise shaping characteristics of $\Sigma \triangle$ ADC                             | 23 |

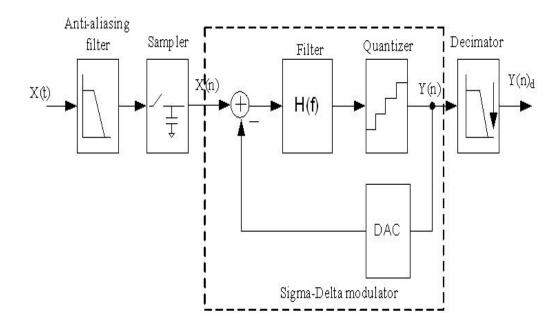

| 2.14 | Block diagram of a noise shaping ADC system                                         | 24 |

| 2.15 | Block diagram of a $\Sigma \triangle$ modulator                                     | 25 |

| 2.16 | Linear model of a $\Sigma \triangle$ modulator                                      | 25 |

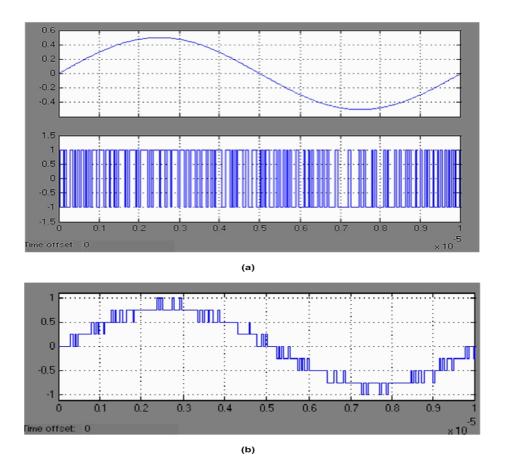

| 2.17 | (a)<br>Input and output waveforms of a first-order $\Sigma\triangle$ modulator with |    |

|      | single-bit quantizer (b) Output waveform of a first-order $\Sigma \triangle$ mod-   |    |

|      | ulator with multi-bit quantizer                                                     | 27 |

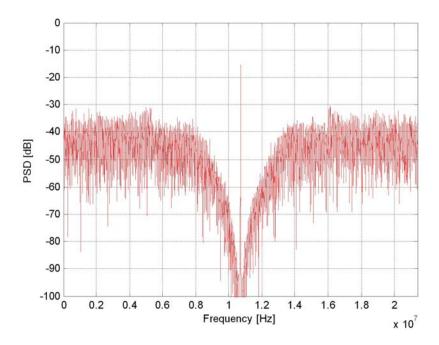

| 2.18 | Output spectrum of a bandpass $\Sigma \triangle$ modulator                          | 28 |

| 2.19 | Definitions of the performance metrics used to characterize a $\Sigma\Delta$      |    |

|------|-----------------------------------------------------------------------------------|----|

|      | ADC                                                                               | 30 |

| 2.20 | The first-order single-loop $\Sigma \triangle$ modulator                          | 31 |

| 2.21 | The second-order single-loop $\Sigma \triangle$ modulator                         | 31 |

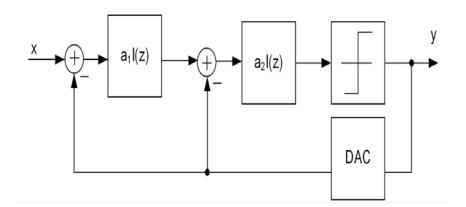

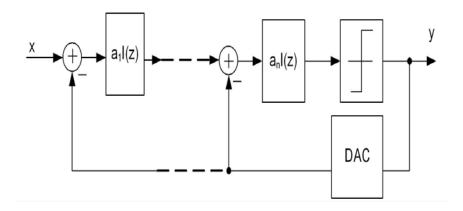

| 2.22 | General block diagram of the n-th order single-loop $\Sigma \triangle$ modulator  | 32 |

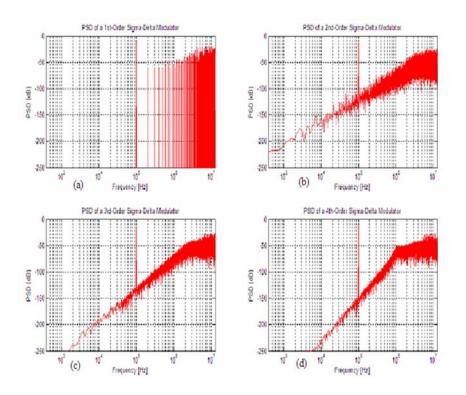

| 2.23 | Figure (a) to (d): Output spectrum of first-order to fourth-order                 |    |

|      | single-loop single-bit $\Sigma \triangle$ modulators                              | 35 |

| 2.24 | Block diagram of the noise cancelling concept                                     | 38 |

| 2.25 | Block diagram of a third-order cascaded 2-1 $\Sigma\triangle$ modulator topology  | 39 |

| 2.26 | Block diagram of a fourth-order cascaded 2-2 $\Sigma\triangle$ modulator topology | 41 |

| 2.27 | Block diagram of a fourth-order cascaded 2-1-1 $\Sigma\triangle$ modulator        |    |

|      | topology                                                                          | 43 |

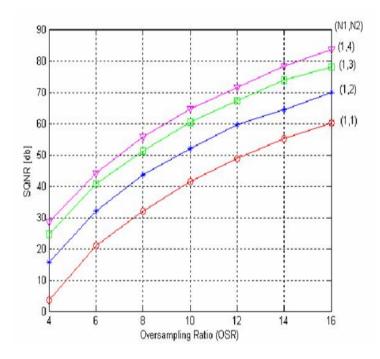

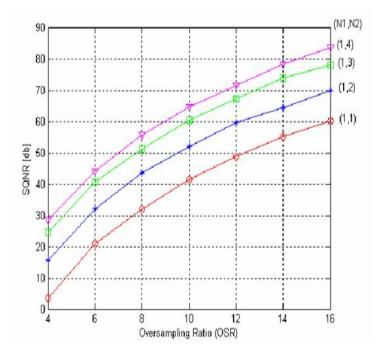

| 2.28 | SQNR vs over<br>sampling ratio for a 2-1 third-order cascaded $\Sigma\triangle$   |    |

|      | topology                                                                          | 44 |

| 2.29 | SQNR vs over<br>sampling ratio for 2-2 (fourth-order) cascaded $\Sigma\triangle$  |    |

|      | topology                                                                          | 45 |

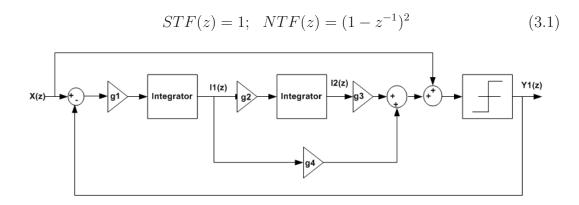

| 3.1  | Low-distortion swing-suppression SDM                                              | 49 |

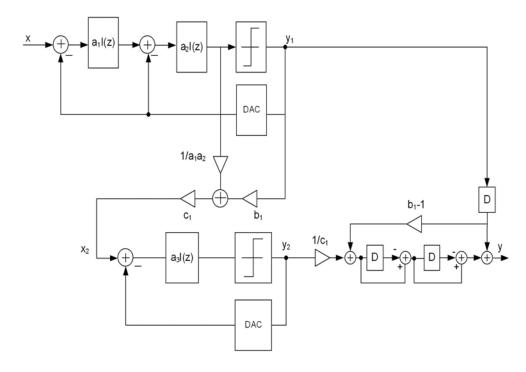

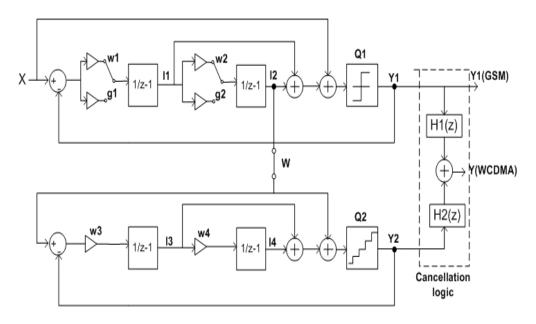

| 3.2  | Dual-mode sigma-delta modulator                                                   | 50 |

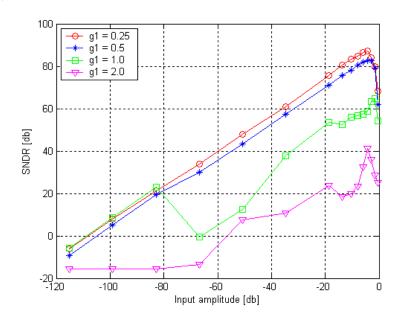

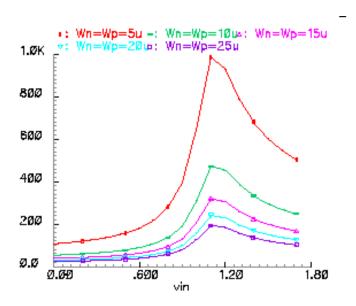

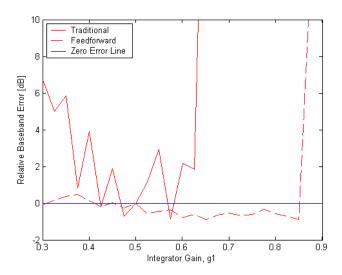

| 3.3  | Sweep of $g_1$ keeping $g_2 = 0.5 \dots \dots \dots \dots \dots \dots$            | 52 |

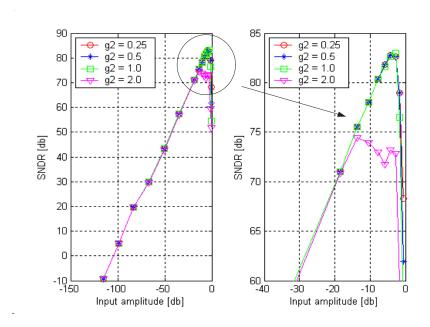

| 3.4  | Sweep of $g_2$ keeping $g_1 = 0.5 \dots \dots \dots \dots \dots \dots$            | 53 |

| 3.5  | PSD of (a) Traditional second-order $\Sigma \triangle$ modulator (b) Feed for-    |    |

|      | ward second-order $\Sigma \triangle$ modulator                                    | 54 |

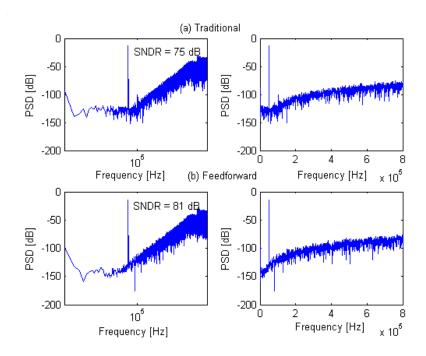

| 3.6  | Comparison of the output swing                                                    | 56 |

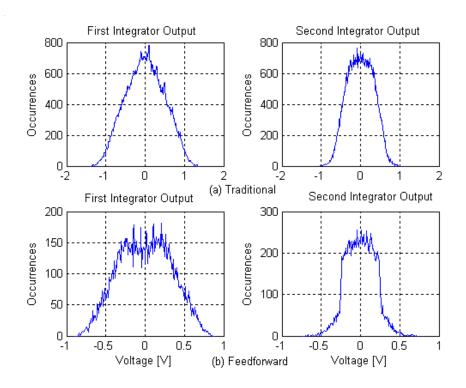

| 3.7  | PSD of traditional cascaded 2-2 and feedforward 2-2                               | 57 |

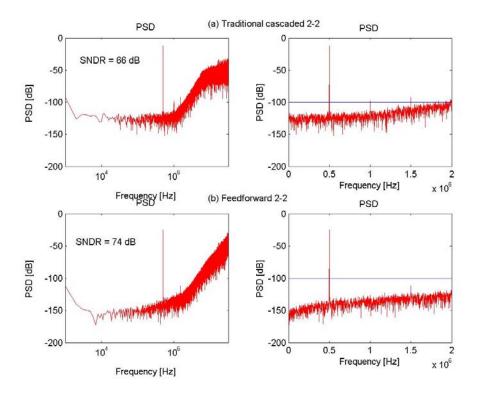

| 3.8  | SNDR versus the input level for GSM and WCDMA architecture                        | 58 |

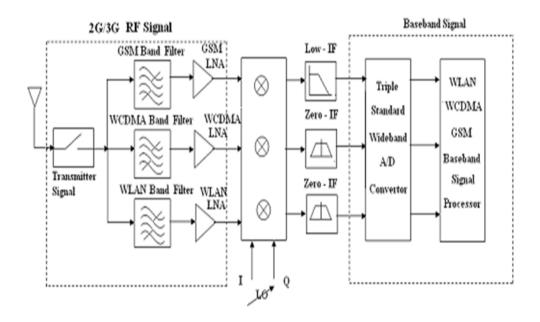

| 3.9  | Triple standard wideband receiver architecture                                    | 59 |

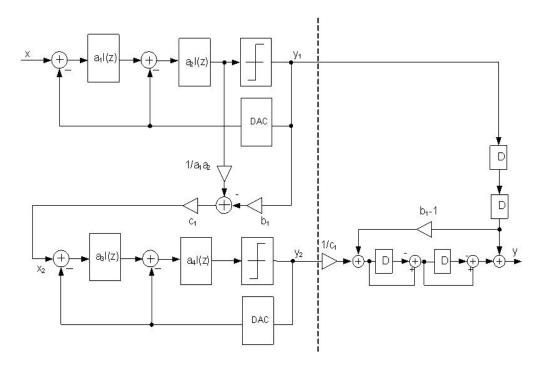

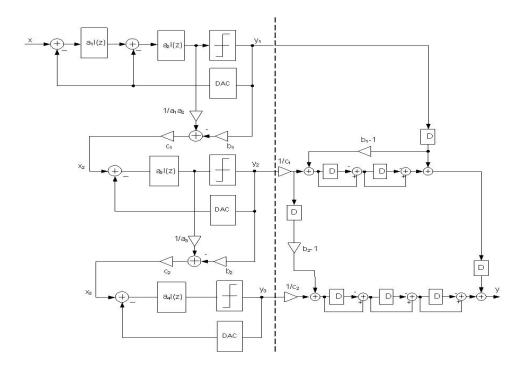

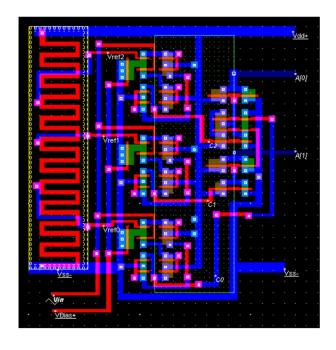

| 3.10 | Programmable $\Sigma \triangle$ modulator for $GSM/WCDMA/WLAN$                    | 61 |

| 3.11 | Modulator output spectrum in GSM mode                                             | 63 |

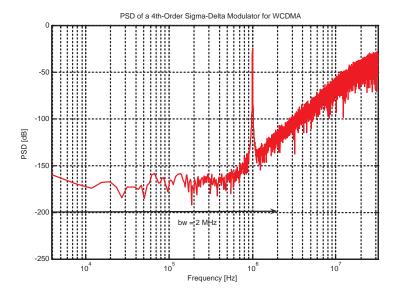

| 3.12 | Modulator output spectrum in WCDMA mode                                           | 63 |

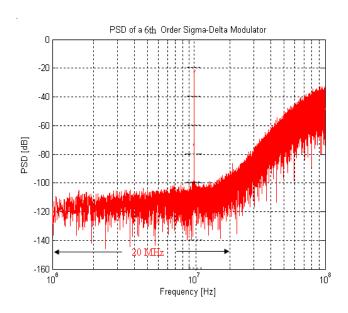

| 3.13 | Modulator output spectrum in WLAN mode                                            | 64 |

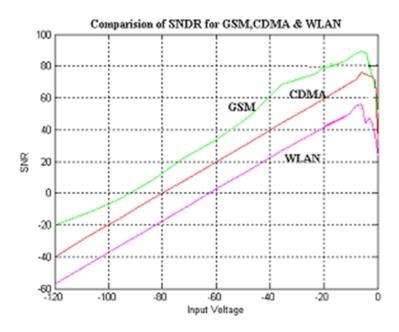

| 3.14 | SNDR versus input level for GSM/WCDMA/WLAN mode                                   | 64 |

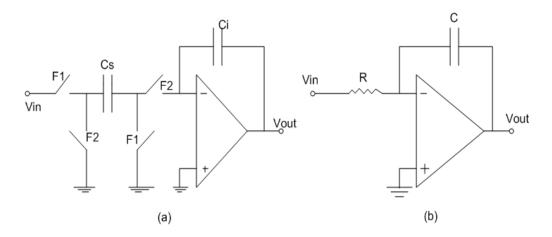

| 4.1  | (a) Switched-capacitor integrator (b) Continuous-time integrator .                | 67 |

### LIST OF FIGURES

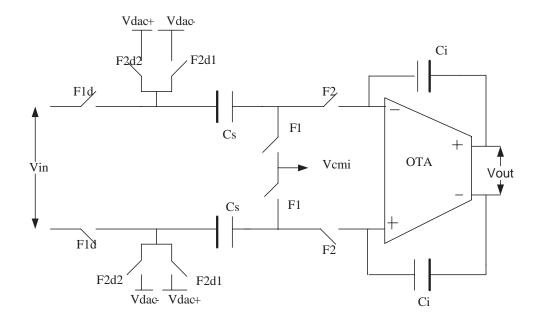

| 4.2  | Fully-differential switched-capacitor integrator                                     | 68  |

|------|--------------------------------------------------------------------------------------|-----|

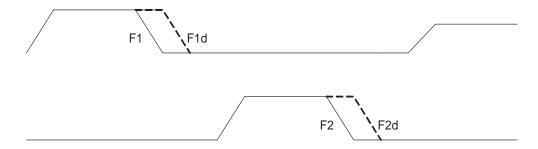

| 4.3  | Two-phase non-overlap clock                                                          | 69  |

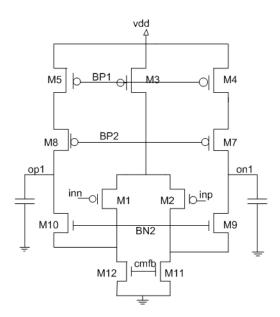

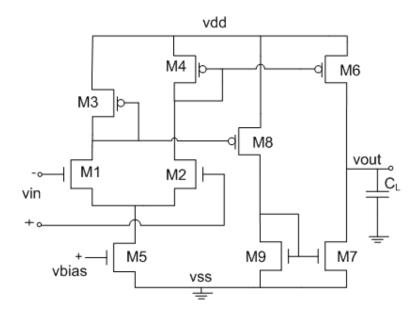

| 4.4  | Fully-differential folded-cascode OTA                                                | 70  |

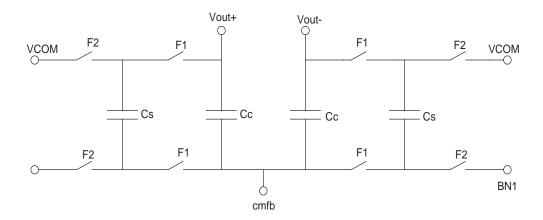

| 4.5  | A switched-capacitor common-mode feedback                                            | 72  |

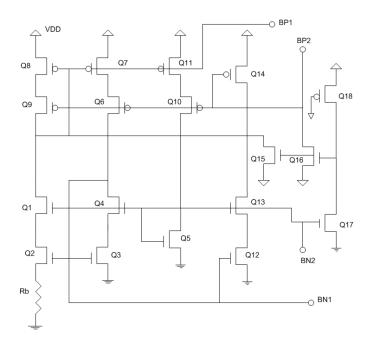

| 4.6  | Wide swing constant transconductance bias circuit                                    | 73  |

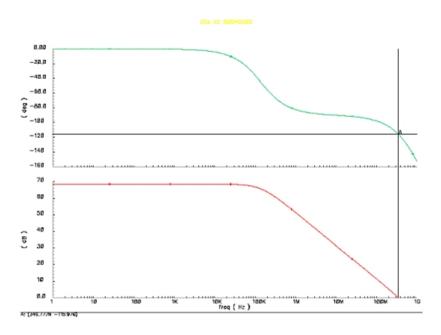

| 4.7  | Frequency response of OTA                                                            | 74  |

| 4.8  | Cascode OTA circuit with high output resistance                                      | 75  |

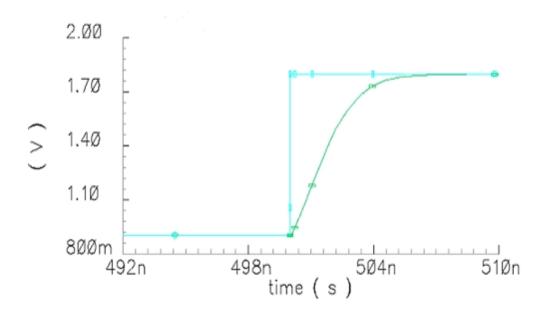

| 4.9  | Transient response of OTA                                                            | 75  |

| 4.10 | Slew rate of OTA                                                                     | 76  |

| 4.11 | Frequency response of OTA corresponding to load capacitance 1fF                      |     |

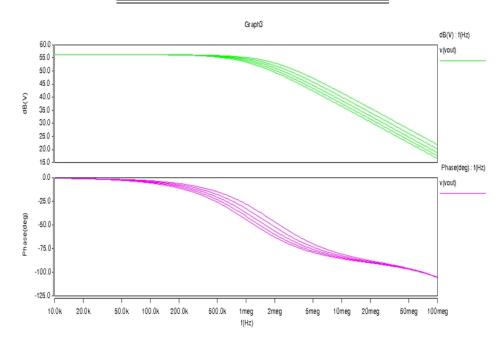

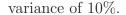

|      | to 10fF                                                                              | 77  |

| 4.12 | Monte carlo simulation of frequency response of OTA with 10 $\%$                     |     |

|      | variation in threshold voltage                                                       | 78  |

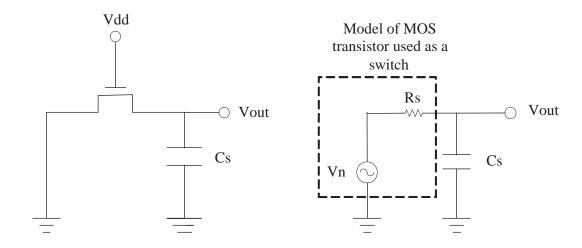

| 4.13 | On-resistance of the sampling switch                                                 | 79  |

| 4.14 | A switched-capacitor sampling network                                                | 81  |

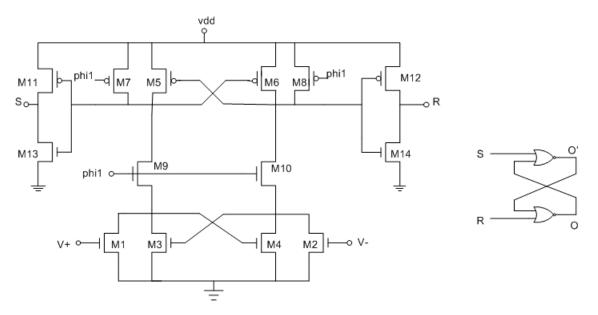

| 4.15 | Regenerative comparator                                                              | 85  |

| 4.16 | Clamped push-pull output comparator                                                  | 86  |

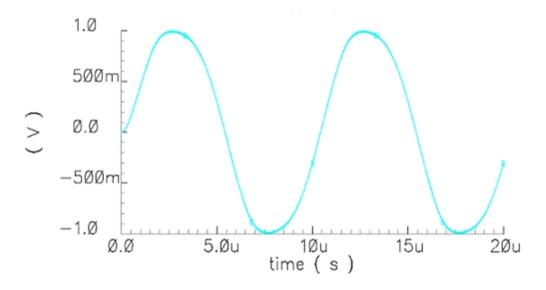

| 4.17 | Time domain simulation of comparator                                                 | 86  |

| 4.18 | Hysteresis of the comparator                                                         | 87  |

| 4.19 | (a) Block diagram of the A/D/A system (b) Partial view of its SC                     |     |

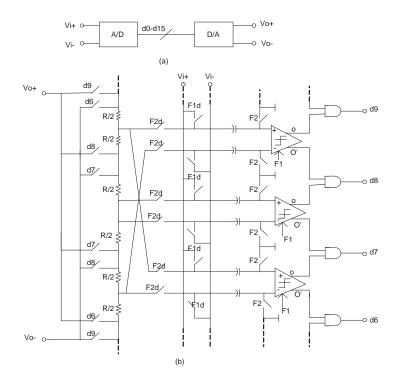

|      | implementation                                                                       | 88  |

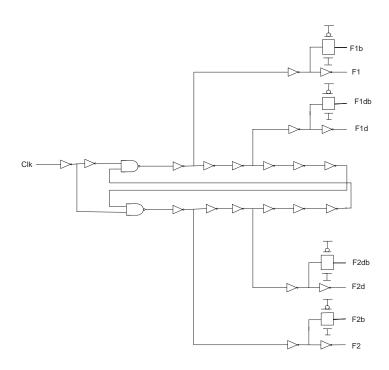

| 4.20 | Two-phase clock generator schematic                                                  | 91  |

| 4.21 | The first stage $2^{nd}$ -order feed-forward single-bit $\Sigma \triangle$ modulator | 91  |

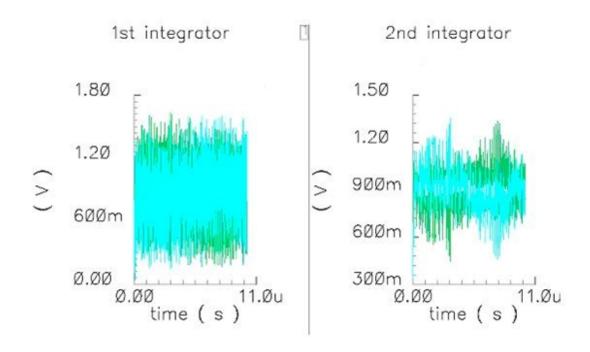

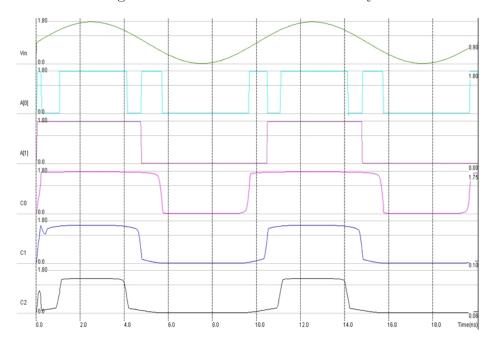

| 4.22 | Time domain plots of $1^{st}$ and $2^{nd}$ integrator                                | 92  |

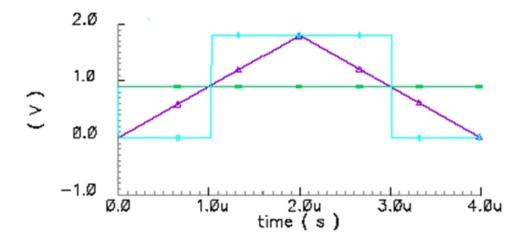

| 4.23 | Modulator response with the modulator input and quantizer output                     | 93  |

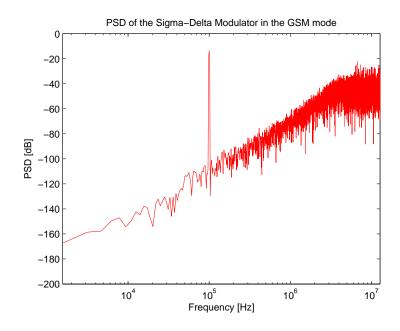

| 4.24 | Output spectrum in GSM mode                                                          | 93  |

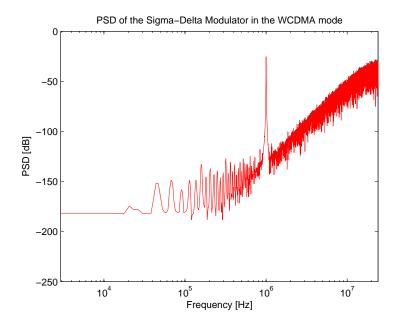

| 4.25 | Output spectrum in WCDMA mode                                                        | 94  |

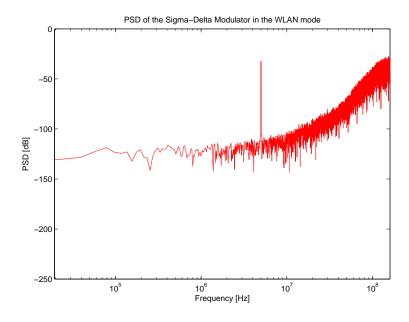

| 4.26 | Output spectrum in WLAN mode                                                         | 94  |

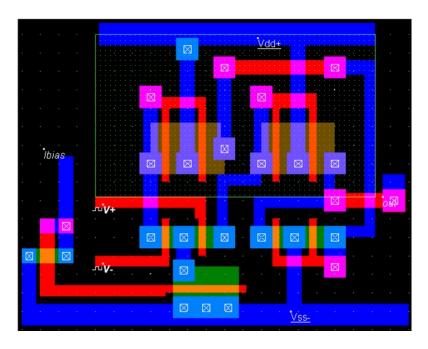

| 4.27 | Opamp layout                                                                         | 95  |

| 4.28 | Two bit flash converter layout                                                       | 96  |

| 4.29 | Two bit flash converter layout simulation output                                     | 96  |

| 5.1  | GUI for Multi-standard Sigma-Delta Modulator Design Toolbox . 1                      | 100 |

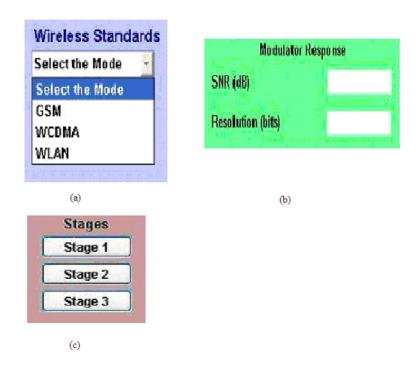

| 5.2  | GUI:(a) Pop-up menu for standard selection; (b) Message box dis-                     |

|------|--------------------------------------------------------------------------------------|

|      | playing the modulator response (c) Button group for stage selection 102              |

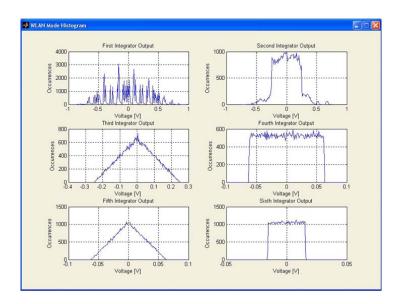

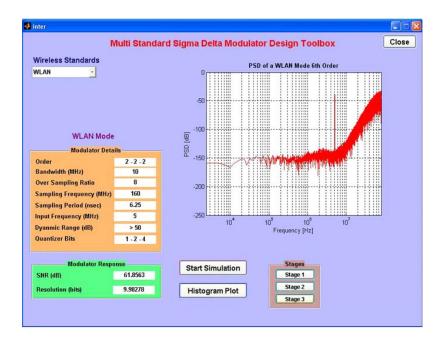

| 5.3  | Histogram plot of the integrator outputs                                             |

| 5.4  | Display of the PSD plot of the selected standard WLAN $\dots 104$                    |

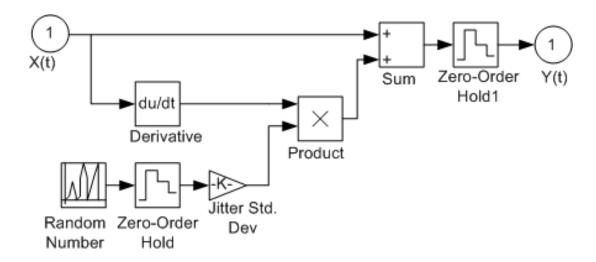

| 5.5  | Modeling a random sampling jitter                                                    |

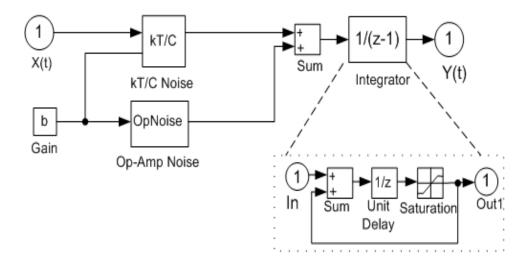

| 5.6  | Model of a 'noisy' integrator                                                        |

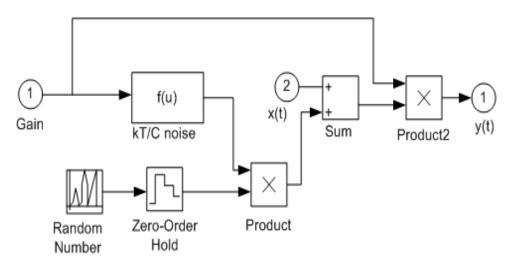

| 5.7  | Modeling switches thermal noise (kT/C) block 106                                     |

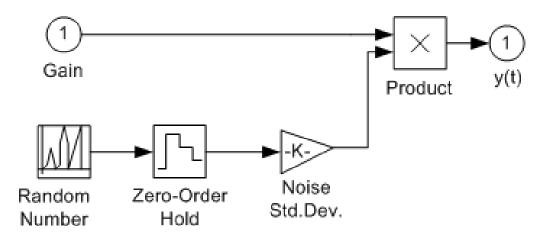

| 5.8  | Opamp noise model                                                                    |

| 5.9  | Simulated influence of variations in integrator gain on base band                    |

|      | quantization noise                                                                   |

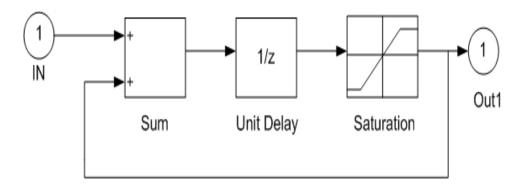

| 5.10 | Ideal integrator                                                                     |

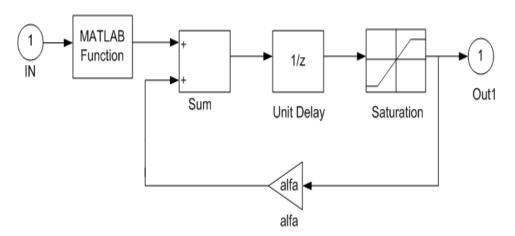

| 5.11 | Real integrator                                                                      |

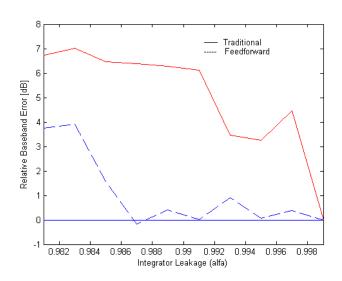

| 5.12 | Influence of integrator leak on baseband quantization noise 110                      |

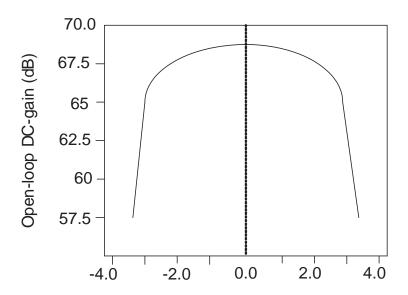

| 5.13 | Open-loop dc gain as a function of the output voltage $112$                          |

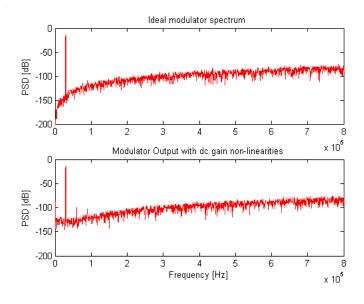

| 5.14 | Simulated influence of dc gain non-linearities on the output spectrum $112$          |

| 5.15 | Simulated coefficient variation: Traditional modulator 113                           |

| 5.16 | Simulated coefficient variation : Feed forward topology 113                          |

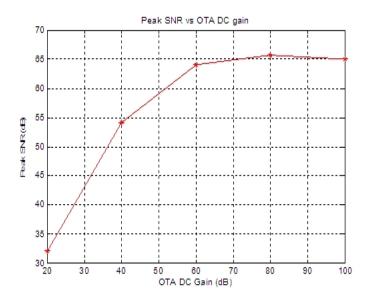

| 5.17 | Peak SNR vs. OTA dc gain                                                             |

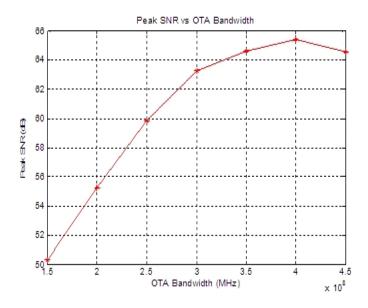

| 5.18 | Peak SNR vs. OTA bandwidth                                                           |

| 5.19 | Peak SNR vs. OTA slew rate                                                           |

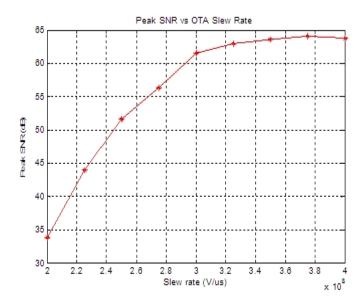

| 5.20 | SNR as a function of the input signal amplitude for different values                 |

|      | of the operational amplifier saturation voltage (Amax) $\dots \dots 116$             |

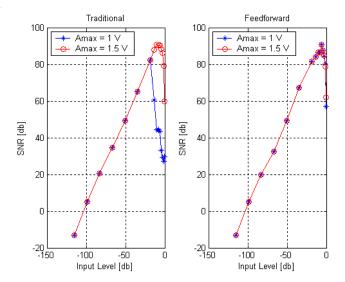

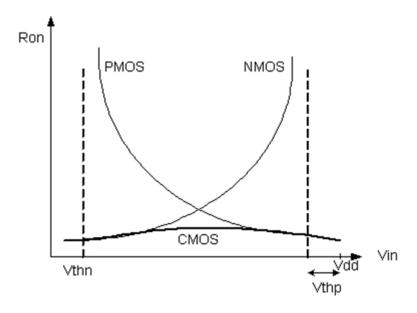

| 5.21 | Switch on-resistance as a function of the input voltage 117                          |

| 5.22 | Distortion of the sampling phase of an integrator                                    |

| 5.23 | Output spectrum of the modulator with and without mismatch $$ . 119                  |

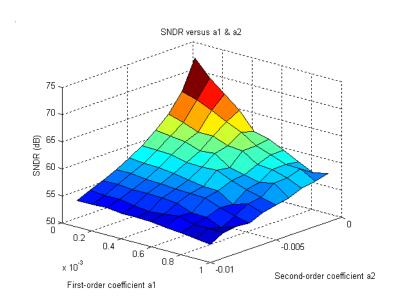

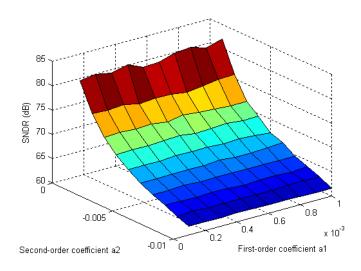

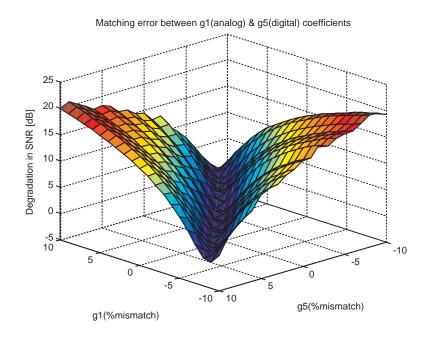

| 5.24 | Degradation in SNR versus $g_1$ and $g_5$                                            |

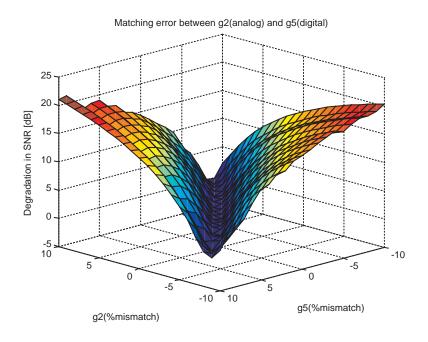

| 5.25 | Degradation in SNR versus $g_2$ and $g_5$                                            |

| 5.26 | Nonlinear D/A model                                                                  |

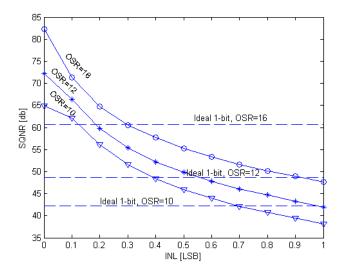

| 5.27 | SQNR vs. INL for a 4th-order cascaded sigma-delta modulator                          |

|      | using 1-bit D/A in the first stage and 4-bit D/A in the second stage.122 $$          |

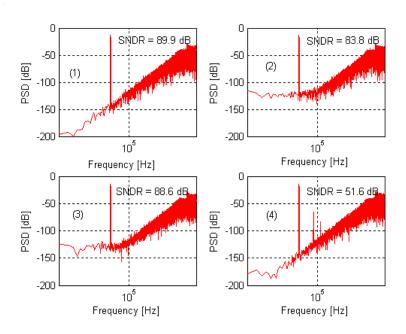

| 5.28 | PSD of (1) the ideal modulator; (2) with sampling jitter, $\tau$ = 4 ns;             |

|      | (3) with $kT/C$ noise, $C_s = 1.25$ pF; (4) with $SR = 50 \text{ V/}\mu\text{s}$ 123 |

### LIST OF FIGURES

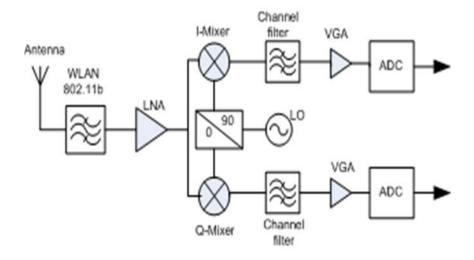

| 6.1  | Zero-IF receiver architecture                                        | 128 |

|------|----------------------------------------------------------------------|-----|

| 6.2  | Modified cascaded sigma-delta modulator for WLAN $\ \ldots \ \ldots$ | 129 |

| 6.3  | Flow chart of binary GA                                              | 132 |

| 6.4  | Single-point crossover process                                       | 134 |

| 6.5  | Convergence of coefficient $g_1$ with number of generations          | 135 |

| 6.6  | Modulator output spectrum for WLAN                                   | 136 |

| 6.7  | SNDR versus input signal amplitude with and without GA               | 137 |

| 6.8  | A traditional second-order sigma-delta topology                      | 137 |

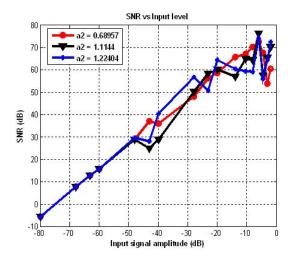

| 6.9  | Convergence of $a_2$ with the number of generations                  | 139 |

| 6.10 | SNR vs. input amplitude for a second-order traditional topology .    | 140 |

# List of Tables

| 2.1 | Specifications of GSM, WCDMA and WLAN standards                   | 10 |

|-----|-------------------------------------------------------------------|----|

| 2.2 | Topology parameters and modulator performance for second to       |    |

|     | fourth-order single-loop single-bit $\Sigma \triangle$ modulators | 36 |

| 2.3 | Topology parameters and modulator performance for second to       |    |

|     | fourth-order single-loop 4-bit $\Sigma \triangle$ modulators      | 37 |

| 2.4 | Topology parameters and modulator performance for the Cascaded    |    |

|     | 2-1 $\Sigma\triangle$ modulator                                   | 42 |

| 2.5 | Topology parameters and modulator performance for the Cascaded    |    |

|     | 2-2 $\Sigma\triangle$ modulator                                   | 42 |

| 2.6 | Topology parameters and modulator performance for the Cascaded    |    |

|     | 2-1-1 $\Sigma\triangle$ modulator                                 | 42 |

| 3.1 | Summary of the published multi-standard $\Sigma\triangle$ ADCs    | 48 |

| 3.2 | Integrator gain coefficients                                      | 55 |

| 3.3 | ADC requirements for multi-standard receiver                      | 59 |

| 3.4 | Comparison of $\Sigma \triangle$ modulator architectures          | 61 |

| 3.5 | Coefficients of the triple-mode sigma-delta modulator             | 62 |

| 3.6 | Performance summary of the triple-mode sigma-delta modulator $.$  | 65 |

| 4.1 | Switches and capacitors in the integrator                         | 69 |

| 4.2 | Transistor sizes of folded-cascode OTA                            | 71 |

| 4.3 | Capacitor sizes in the switched-capacitor CMFB                    | 72 |

| 4.4 | Transistor sizes in the bias circuitry                            | 73 |

| 4.5 | Performance summary of the folded-cascode OTA                     | 77 |

| 4.6 | Transistor sizes in the regenerative latch                        | 85 |

## LIST OF TABLES

| 4.7 | Performance comparison with other multi-standard $\Sigma\triangle$ ADCs $$ | 97  |

|-----|----------------------------------------------------------------------------|-----|

| 5.1 | Performance summary for GSM, WCDMA and WLAN Mode $$                        | 124 |

| 6.1 | Radio specifications for WLAN 802.11b                                      | 128 |

| 6.2 | Comparison of gain coefficients with and without GA $\dots$                | 136 |

| 6.3 | Second example: Coefficients                                               | 139 |

# Chapter 1

## Introduction

### 1.1 Motivation

Rapid evolution of digital integrated circuit technologies has led to sophisticated signal processing systems. Future mobile systems will be able to communicate with various heterogeneous systems which are different by means of the algorithms used to implement baseband processing. This may pose many challenges in designing flexible, energy efficient and adaptable architectures. Moreover, demand for new telecommunication services requiring higher capacities, data rates and different operating modes have motivated the development of new generation multistandard wireless transceivers. Transceivers for multi-mode and multi-standard telephony are often implemented by replicating the receiver circuits for each operating band or standard (89),(1). By using conventional receiver architectures, simultaneous operation at different frequencies can only be achieved by building multiple independent signal paths which may eventually increase the cost and power dissipation. Therefore, multi-standard receivers often re-use circuit blocks, or multiple RF front-ends (i.e., one for each standard if necessary). To achieve higher data rates in emerging wireless generations, (for example WCDMA, IEEE 802.11b), the analog front-end must be able to handle wider bandwidths at lower noise and power levels. Efficient integration can be obtained by using receiver architectures and circuit techniques that eliminate the need for external components. Utilizing a receiver architecture that performs channel select filtering on chip at baseband allows for the programmability necessary to adapt to multiple communication standards.

The most important component for the success of multi-mode systems has been the analog-to-digital converter (ADC) that converts continuous time signals to a discrete time, binary coded form for later digital signal processing. Different signal types to be digitized has led to a diverse selection of data converters in terms of architectures, resolution and sampling rates. In the wireless communications arena transmitters and receivers and ADC in particular, have to cope with the requirements imposed by many different standards operating in the same geographical zone, making it necessary for mobile communications equipment to manage multiple standards. A direct conversion of a radio frequency signal to the digital domain directly at the receiver antenna or after some amplification stages will give efficient multi-standard architectures implementation. In digital domain, all other operations to detect and recover the desired signal are performed in a fully digital fashion, by means of programmable hardware. This would allow the upgrading of a mobile terminal completely by software following the evolution of the communications standards, as well as its adaptability to different operating environments. To meet the above requirements analog-todigital converter requirements on sampling linearity, conversion rate, resolution, and power consumption are becoming stringent. In general, in order to achieve a wide bandwidth and a high resolution, the sampling frequency, the noise-shaping order and the quantizer resolution should be increased (89), (93).

The sigma-delta (64), (46), (5) analog-to-digital converters (ADCs) are widely used in wireless systems because of their superior linearity, robustness to circuit imperfections, inherent resolution-bandwidth trade off and increased programmability in digital domain. Sigma-delta modulator is the most promising candidate to achieve high resolution over a wide variety of bandwidth requirements in multimode receivers. Many of the desired integration aspects can be satisfied with sigma-delta converter front-ends. The advantage of sigma-delta ADCs in providing high resolution with low precision components lies on the use of over-sampling and noise shaping. As bandwidth requirement increases, the over-sampling ratio decreases which results in a decrease in the resolution. Designing sigma-delta

modulators that can achieve high resolution and wide bandwidth remains challenging. These solutions based on switched-capacitor (SC) based implementation cover a wide variety of wireless standards like GSM, WCDMA, WLAN etc.

In modern deep-submicron CMOS processes, the ultimate goal is to reduce cost using a single chip solution (system on a chip (SoC)). This brings the additional design challenges in the data converter design, such as decreasing supply voltage, short channel effects (65) in MOS devices, and matching of devices. Therefore, the requirements of sampling linearity, process matching, high DC gain and high gain-bandwidth product opamps in the traditional data converter architectures are becoming more and more difficult to be realized. The performance requirements of analog circuits should be significantly relaxed, so that sigma-delta ADC architectures are suitable for realizing high resolution broadband ADCs with new technologies (24), (45), (8), (86). In this scenario, a novel low-distortion multi-bit sigma-delta modulator with improved performance is indeed essential. This motivates the development of various design techniques considering various non-idealities.

#### 1.1.1 Research Focus

This work focused on the analysis, design techniques and optimization of over-sampled sigma-delta ADCs aimed for multimode wireless receivers. Even though the properties of oversampling ADC converters are well known, the increasing bandwidth of the signals to be converted in the communications systems, as well as the required resolution imposed by the standards, require high oversampling ratios. ADCs with higher sampling frequencies and low power consumption is a design challenge, which is an essential constraint of portable systems.

## 1.2 Author's Contributions

The primary technical contributions of this thesis are in the area of developing design techniques for sigma-delta ADC for multi-standard wireless transceivers. An investigative study was conducted to develop a tool box for the modeling and

analysis. Additionally, a methodology is also developed for coefficient optimization using genetic algorithms. The main contributions and the papers on which they are based are listed below.

- **J1. Babita Roslind Jose**, J. Mathew, P. Mythili, "A Multi-mode Sigma-delta ADC for GSM/WCDMA/WLAN Applications," in *Journal of Signal Processing Systems (Springer)*, DOI10.1007/s11265 008 0326 z, ISSN:1939-8018, January 2009.

- C1. Babita Roslind Jose, J. Mathew, P. Mythili, "A Triple-mode Feed-forward Sigma-delta Modulator Design For GSM / WCDMA / WLAN Applications", 20th IEEE International System On Chip Conference (IEEE SOCC 2007), September 2007.

Author's Contribution: A new low-distortion triple-mode architecture for multi-standard receivers is proposed. This topology is less sensitive to circuit imperfections compared with the traditional one, suitable for wideband applications where low oversampling ratios are used. The author came up with the concept, theoretical formulations and simulations, and wrote the manuscript. The concise version is presented in the conference and extended version is published in the journal.

- **J2.** Babita Roslind Jose, J. Mathew, P. Mythili, "Dual-Band Sigma-delta ADC for WCDMA/WLAN Receivers", in *International Journal of Applied Engineering and Research*, vol 3, pp.257-273, 2008.

- **C2.** Babita Roslind Jose, J. Mathew, P. Mythili, "A Low Power Programmable Sigma-Delta Modulator for Dual-Band Multi-Mode Receivers", *International Conference on Embedded Systems and Applications (ESA'07)*, 2007.

Author's Contribution: A programmable sigma-delta modulator for dualband multi-mode receivers is proposed, which is less sensitive to circuit imperfections compared with the conventional architectures. The author came up with the concept, theoretical formulations and simulations, and wrote the manuscript. The concise version is presented in the conference and extended version is published in the journal.

**J3.** Babita Roslind Jose, J. Mathew, P. Mythili, "Wideband Low-Distortion Sigma-Delta ADC For WLAN With RNS Based Decimation Filter", in *IETECH*

Journal of Information Systems, International Engineering & Technology Publications, vol.2, No.2, pp.68-75, 2008.

C3. Babita Roslind Jose, Shahana T K, P. Mythili, "Wideband Low-Distortion Sigma-Delta ADC For WLAN With RNS Based Decimation Filter", *IET International Conference on Information and Communication Technology in Electrical Sciences (ICTES 2007)*, Chennai, December, 2007.

Author's Contribution: A highly linear sigma-delta ADC with a high speed computationally efficient RNS (Residue Number System) based decimation filter is proposed for WLAN applications. The low-distortion topology has reduced sensitivity to OTAs (Operational Transconductance Amplifier) nonlinearity effects and simplifies the implementation of cascaded architecture. The author came up with the concept, theoretical formulations and simulations, and wrote the manuscript. Co-author developed decimation filter. The concise version is presented in the conference and extended version is published in the journal.

- **J4.** Babita Roslind Jose, J. Mathew, P. Mythili, "GA-based Optimization of Sigma-delta Modulators for Wireless Transceivers" in *Engineering letters*, vol 16, no.4, pp.473-479, 2008.

- C4. Babita Roslind Jose, J. Mathew, P. Mythili, "GA-based Optimization of a Fourth-order Sigma-delta Modulator for WLAN". *IEEE International Conference on Systems, Man & Cybernetics*, 12-15 October 2008, Singapore, 2007.

Author's Contribution: A new optimization technique using Genetic Algorithm is proposed. This approach gives better and fast optimization of modulator coefficients. The author came up with the concept, theoretical formulations and simulations, and wrote the manuscript. The concise version is presented in the conference and extended version is published in the journal.

C5. Babita Roslind Jose, Shahana T.K., P. Mythili, "GUI-based Sigmadelta Modulator Design Tool for Multi-standard Wireless Transceivers", *National Conference On Communication Engineering, Signal Processing and VLSI Design*, 16-18 December 2009, Cochin, India.

Author's Contribution: A new tool box is developed to aid design and analysis of multi-standard sigma-delta modulator design. This toolbox will help

the user to do a quick design and analysis. The author came up with the concept and developed the tool box. The concise version is presented in the conference and a journal version is under preparation.

### 1.2.1 Other Contributions not Included in this Thesis

- J1. Shahana T. K, Babita R. Jose, Rekha K. James, K. Poulose Jacob, Sreela Sasi, "RNS based Programmable Decimation Filter for Multi-Standard Wireless Transceivers," in *ECTI Transaction on Electrical Engineering, Electronics and Communications, ECTI-Transaction Journal, Vol. 6, No. 2, pp. 57-66, 2008.*

- **J2.** Shahana T. K, **Babita R. Jose**, Rekha K. James, K. Poulose Jacob, Sreela Sasi, "A Novel Sigma-Delta based Parallel Analog-to-Residue Converter," in *International Journal of Electronics, Taylor and Francis, 2009.*

- J3. Shahana T. K, Babita R. Jose, K. Poulose Jacob, Sreela Sasi, "RRNS-Convolutional Concatenated Code for OFDM based Wireless Communication with Direct Analog-to-Residue Converter," in *International Journal of Electrical, Computer and Systems Engineering, World Academy of Science, Engineering and Technology, Vol. 2, No. 2, Spring 2008, pp.86-93, 2009.*

- **J4.** Shahana T. K, **Babita R. Jose**, Poulose Jacob, Sreela Sasi, "Decimation Filter Design Toolbox for Multistandard Wireless Transceivers using Matlab," in *International Journal of Signal Processing, Volume 5, Number 2, 2009*.

- C1. Shahana T. K, Babita R. Jose, Rekha K. James, K. Poulose Jacob, Sreela Sasi, "Dual-Mode RNS based Programmable Decimation Filter for WCDMA and WLANa," in *IEEE International Symposium on Circuits and Systems (ISCAS 2008)*.

- C2. Shahana T. K, Babita R. Jose, Rekha K. James, K. Poulose Jacob, Sreela Sasi, "RNS based Programmable Multi-mode Decimation Filter for WCDMA and WiMAX," in *IEEE 67th Vehicular Technology Conference: VTC 2008-Spring*, 11-14 May, Singapore.

- C3. Shahana T. K, Babita R. Jose, Rekha K. J., K. Poulose Jacob, Sreela Sasi, "RRNS-Convolutional encoded Concatenated Code for OFDM based

Wireless Communication," in 16th IEEE International Conference on Networks (ICON 2008), New Delhi, India, 12-14 December 2008.

C4. Shahana T. K, Rekha K. J., Babita R. Jose, K. Poulose Jacob, Sreela Sasi, "Polyphase Implementation of Non-recursive Comb Decimators for Sigma-Delta A/D Converters," in *IEEE International Conference on Electron Devices and Solid-State Circuits*, Taiwan, December 20-22, 2007.

### 1.3 Thesis Outline

Chapter 2 provides the background material relevant to this thesis. Since, majority of the techniques described in this thesis is for Ato D converters, in particular sigma-delta ADC, the basics of sigma-delta analog-to-digital converters is reviewed.

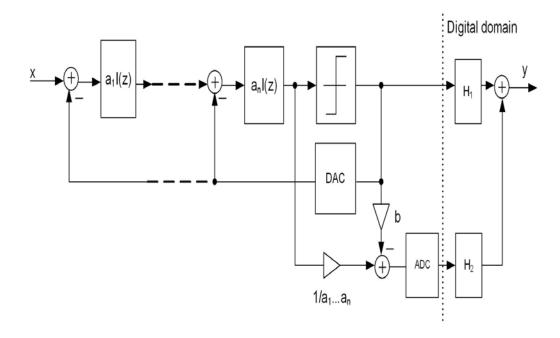

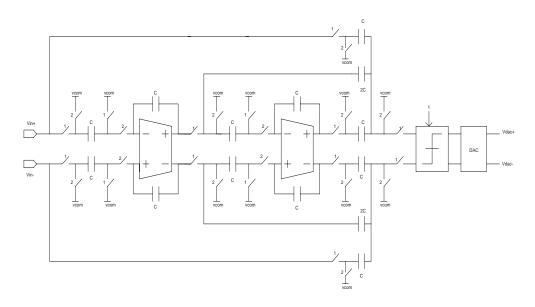

Chapter 3 describes system level design of a re-configurable sigma delta analog-to-digital converter for three wireless communication standards namely GSM, WCDMA and WLAN, which reduces the overall system complexity in software defined radios. A low-distortion swing suppression topology has been selected for our architecture which has reduced sensitivity to op-amp non-linearities, especially at low oversampling ratios. The expressions for the coefficients are derived from the fundamentals. The triple mode design, when compared with existing techniques, gives better performance. This chapter also describes a dual mode design for GSM and WCDMA. Chapter 4 deals with configurable sigma-delta modulator implementation. The proposed sigma-delta modulator for GSM/WCDMA/WLAN receiver was implemented as a fully-differential switched-capacitor (SC) circuit which has been simulated using SPICE. The design of the individual circuit blocks like operational transconductance amplifier (OTAs), switches, capacitors and comparators are described.

Chapter 5 introduces a design tool box for sigma delta converters. A Matlab $^{TM}$  based toolbox help the designers to choose appropriate architecture based on the requirement. To mitigate the design time, various architectures have been designed using Simulink. Various non-linearity models are also incorporated into the tool.

Chapter 6 describes genetic algorithm which is used for the identification of the best coefficients suitable for the proposed sigma-delta topology in order to achieve the desired signal-to-noise ratio. GA-based search engine is a stochastic search method which can find the optimum solution within the given constraints.

The last chapter summarises the work presented in this thesis and provides an outlook of future work.

# Chapter 2

# Background

Mobile communication has seen a tremendous explosive growth since 1983. The recent advances in technologies for wireless access, digital signal processing, integrated circuits, and increased battery life have continued the exponential growth in mobile and personal communication services. The need for multi-mode cellular handsets that support a wide range of communication standards, each with a different RF frequency, signal bandwidth, modulation scheme, etc. is currently driving worldwide research towards the implementation of fully integrated multi-standard transceivers. In order to allow the user to switch seamlessly among different standards, the so-called "global roaming" for both voice and data applications, all these standards have to be supported by an integrated transceiver.

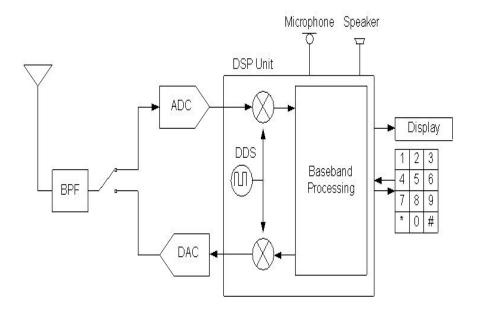

Software defined radios (SDRs) have become a promising solution to support multiple competing and incompatible air interface standards in future wireless communications. The ideal architecture for multi-standard transceiver is the software radio as shown in Figure 2.1 (54). The transceiver incorporates most of the functionality in software as possible, along with the flexibility of maximum hardware sharing of the transceiver building blocks which will help us to reduce cost as well as power consumption. Thus re-configurability is a major concern in multi-standard receiver design while meeting the design specification of the various standards. This in turn generates several design challenges for the analog and digital building blocks.

Sigma-delta analog-to-digital converters (SD-ADCs) are widely used in multistandard transceivers to adapt to the requirements of different standards. Sigma-

Figure 2.1: Ideal software radio transceiver

delta ADC is one of the promising candidate to achieve high resolution over a wide variety of bandwidth requirements in multi-mode receivers. Based on the multi-standard approach, some important specifications of GSM, WCDMA and WLAN (IEEE 802.11b) are collected and listed in Table 2.1 (54).

Taking into account the above considerations, different receiver architectures are discussed focusing on the feasibility of fully integrated implementation for multi-standard solution (42).

Table 2.1: Specifications of GSM, WCDMA and WLAN standards

|                | Frequency          | Channel | Modulation   | Duplex | Channel             |

|----------------|--------------------|---------|--------------|--------|---------------------|

|                | range              | Spacing | Scheme       |        | bandwidth           |

| GSM 900        | Tx- 890 - 915 MHz  | 200 KHz | GMSK         | FDD    | 190 KHz             |

|                | Rx- 935 960 MHz    |         |              | TDD    |                     |

| WCDMA          | Tx- 1920-1980 MHz  | 5 MHz   | QPSK         | FDD    | $3.84~\mathrm{MHz}$ |

| (UMTS)         | Rx-2110 - 2170 MHz |         |              |        |                     |

|                | Tx, Rx             |         | 1Mbps: DBPSK |        |                     |

| WLAN           | 2.4, 2.4835  GHz   | 25 MHz  | 2Mbps: DQPSK | TDD    | $22~\mathrm{MHz}$   |

| (IEEE 802.11b) |                    |         | 5.5Mbps: CCK |        |                     |

|                |                    |         | 11Mbps: CCK  |        |                     |

### 2.1 Radio Receiver Architectures

In this section, we discuss the receiver at the architectural level. Complexity, cost, power dissipation and integration level have been the primary criteria in selecting transceiver architecture. Furthermore, multi-standard capability is another important factor (54), (6), (27)

Figure 2.2: Superheterodyne receiver

## 2.1.1 Superheterodyne Receiver

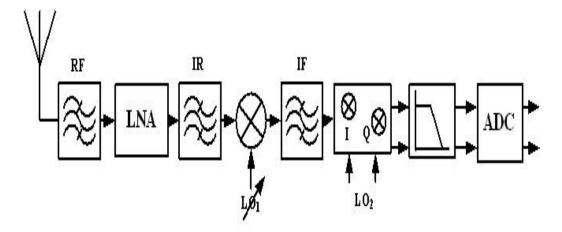

A conventional architecture choice is the superheterodyne receiver shown in Figure 2.2. Here the incoming RF signal received by the antenna is sent through an RF filter and a low noise amplifier (LNA) which amplifies the received signal. An image reject (IR) filter removes any image frequencies present which is then given to a mixer. Then mixing with a tunable LO signal at RF down converts the selected channel to IF. An off-chip, high-Q band pass filter performs partial channel filtering at a relatively high intermediate frequency. A second down conversion mixing step translates the signal down to baseband and further reduces the requirements for the final, integrated channel selection filter. Therefore, the use of a RF (Radio Frequency), IR (Image Rejection) and IF (Intermediate Frequency) filters turns this architecture unsuitable for integration and consequently for multi-standard purposes that would require even more off-chip filters.

### 2.1.2 Direct Conversion Homodyne Receiver

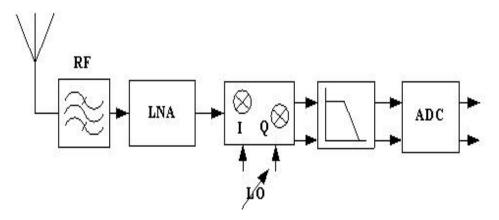

The homodyne architecture shown in Figure 2.3 uses a single frequency translation step to convert the RF channel directly to baseband without operations at intermediate frequencies. It is therefore also called zero-IF or direct conversion architecture. Channel selection is done by tuning the RF frequency of the LO to the centre of the desired channel, making the image equal to the desired channel. Hence, the problem of images is not present, and the off-chip IR filter can be omitted. A subsequent channel selection low-pass filter (LPF) then removes nearby channels or interferers prior to A/D conversion. Thus channel filtering is now possible entirely on-chip due to direct conversion to DC. Therefore, the direct conversion receiver is more suitable for higher integration and multi-standard operation. On the other hand, DC offset and flicker noise are the problems associated with this type of architectures.

Figure 2.3: Direct conversion homodyne receiver

#### 2.1.3 Low-IF Receiver

The low IF receiver shown in Figure 2.4 converts the received RF signal to a low intermediate frequency, eliminating the problems of DC offset and 1/f noise associated with the direct conversion. A low IF on-chip bandpass filter is used to perform baseband channel selection. Besides maintaining the same level of integration as the Zero-IF, multi-standard ability is affected, since the more severe

constraints are posed on bandpass filter and ADC for wide channel bandwidth, leading to an increase in power consumption.

Figure 2.4: Low-IF receiver

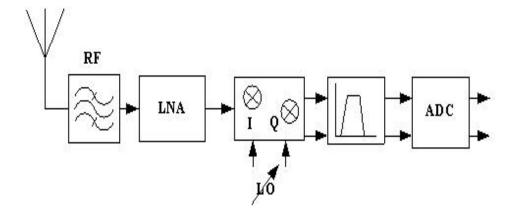

#### 2.1.4 Wideband IF Double-conversion Receiver

An alternative architecture well suited for integration of the entire receiver is wideband IF with double conversion shown in Figure 2.5. This receiver employs a two-step conversion from RF to IF and from IF to DC. Though the first mixer with fixed LO frequency, the RF frequency signal goes down to the IF and then straight to baseband with another programmable mixer. This architecture combines the strengths of heterodyne and homodyne receivers and, it has a high degree of integration and programmability suitable for multi-standard operation. This architecture also suffers from DC offsets as in homodyne receivers.

Analog-to-Digital Converters (ADC) is one of the fundamental building block in any transceiver architecture. As a bridge between the analog-to-digital world, the ADC functions as a translator from an analog quantity to a digital code. There are many types of ADCs and each of them has its own advantages and shortages. Among them the sigma-delta  $\Sigma\Delta$  ADC features high resolution without requirement of high-precision devices, making it a popular choice of high resolution ADCs in cheap CMOS technologies.

Figure 2.5: Wideband IF double conversion receiver

## 2.2 Analog-to-digital Converters

For an ADC, the most important parameters are input signal bandwidth and the resolution. Illustrated in Figure 2.6, there are many applications that need different input signal bandwidth and resolution parameters. Different types of ADCs are developed according to different requirements. The Figure 2.6 also shows different types of ADC that can be used for different applications. The  $\Sigma\Delta$  ADC is suitable for high resolution low-speed applications such as industrial measurement, voiceband, audio where the conversion speed is normally less than a few hundred Hz (92), (78). For conversion speeds of 100KHz to 1MHz, successive approximation ADC find its best position. For higher conversion speeds, the pipelined ADC is suitable and the resolution is normally around 10-12 bit. For conversion speed of 1GHz and above, it is the area of the Flash ADC. So there is a speed and resolution trade-off in ADC performance, which can be seen from Figure 2.6 (43).

## 2.3 Classification of ADC

The ADCs are generally classified as Nyquist rate ADCs and Oversampling ADCs based on the rate at which the signal is sampled relative to the signal bandwidth.

Figure 2.6: Different ADC architectures, applications, resolution and sampling rates

## 2.3.1 Nyquist rate ADCs

Nyquist rate ADCs sample the signal at approximately twice the signal bandwidth, which is the minimum rate required for the reconstruction of the signal according to sampling theorem. Nyquist rate ADCs are fast, but their resolution is limited to 10-12 bit range due to stringent component matching and circuit non-idealities. Also, the antialiasing filter requires a very sharp cut off to avoid aliasing. Examples of Nyquist rate ADCs are flash ADC, successive approximation ADC, pipelined ADC etc, whose conversion rates are constrained by the bandwidth limitations imposed by the implementation technology (35).

## 2.3.2 Oversampling ADCs

Oversampling ADCs sample the analog input signal at a rate much higher than the Nyquist rate. The ratio of the sampling rate and the Nyquist rate is called the oversampling ratio (OSR). ADCs exchange resolution in time for resolution in amplitude (4) in order to ease the demands on the precision with which the signal must be quantized. This class of ADCs do not require stringent component matching requirements and hence are more suitable for high resolution applications (upto 20-bits or more). In Nyquist-rate converters, each digital word is obtained from an accurately quantized input samples, whereas in oversampled converters, each output is obtained from a sequence of coarsely quantized input samples. Oversampling converters take advantage of todays VLSI technology providing high-speed/high-density digital circuits rather than accurate analog circuits by performing most of the conversion process in the digital domain. The analog part of these converters is relatively simple and occupies a small area, unlike their Nyquist rate counterparts. Most implementations use switched capacitor techniques. In the state-of-the art oversampling ADCs, oversampling ratio is typically between 8 and 256. Another advantage is very relaxed requirement on the analog antialiasing filter because of the high sampling rate. Sigma-delta ADC is an oversampling ADC in which oversampling and noise shaping are the two key techniques used to achieve high accuracy.

## 2.4 Basic Analog-to-Digital Conversion

Signals that are progressing continuously in time and amplitude are classified as analog signals. An analog-to-digital converter (ADC) produces a digital representation of the analog input signal by sampling the input signal at discrete time moments and quantizing the amplitude of the input signal in discrete amplitude levels (4). Thus the A/D conversion includes two procedures: 1) sampling, to make the signal discrete in time and 2) quantizing, to make the signal discrete in amplitude (66). Accordingly there are two important specifications for an ADC: speed and resolution. The speed represents how fast the discretization in time can be done. The resolution represents how accurate the discretization in amplitude can be done. ENOB (Effective Number of Bit) is often used to characterize the conversion resolution. Figure 2.7 shows the block diagram of an ADC.

The antialiasing filter is used to limit the bandwidth of the analog input to less than half of the sampling frequency. This ensures that the sampling operation will not alias noise or out-of-band signals back into the baseband of the ADC.

Figure 2.7: Block diagram of analog-to-digital conversion

The width of the antialias filters transition band increases with the sampling rate relative to input signal bandwidth (BW). The quantized signal is digitally encoded based on the resolution which in turn dictates the quantization error.

### 2.4.1 Sampling

Figure 2.8 shows the sampling operation. Ideal uniform sampling of a continuoustime, band-limited signal, x(t) corresponds to a multiplication of that signal by an ideal impulse train which results in a sampled signal  $x_s(t)$  with uniformly spaced samples obtained at nT, where T is the inverse of the sampling frequency,  $f_s$ . The sampled signal  $x_s(t)$  can be described as a continuous time signal by

$$x_s(t) = \sum_{n=-\infty}^{n=\infty} x(t)\partial(t-nT), \quad where \quad \partial(t-nT) = \left\{ \begin{array}{l} 1, t = nT \\ 0, t \neq nT \end{array} \right\}$$

(2.1)

In the frequency domain this is equivalent to convolving the input spectrum with a train of impulses and results in images of the input spectrum centered at integer multiples of the sampling frequency as shown in Figure 2.8.

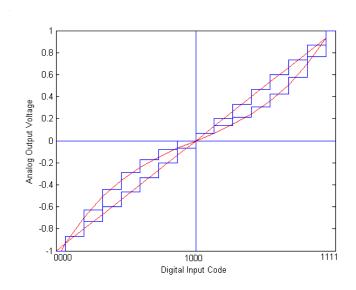

## 2.4.2 Quantization

Quantization is the discretization in amplitude as shown by the characteristic curve of Figure 2.9(a). For an ADC, there is always an error  $e_q$  defined by equation 2.2 associated with the ADC. This error is called quantization error. The higher resolution the ADC is, the smaller quantization error it has. Since

Figure 2.8: Sampling operation (a) in time domain (b) in frequency domain

the process of quantization is a classification process in amplitude, there is always a quantization error in an ADC, as shown in Figure 2.9(b). The quantization error  $e_q$  is smaller than the quantization step  $\Delta$  of the ADC.

$$e_q = y - x \tag{2.2}$$

$$-\frac{\Delta}{2} \le e_q \le \frac{\Delta}{2} \tag{2.3}$$

The quantization step  $\Delta$ , with a value of  $V_{ref}/2^N$  is called the least significant bit (LSB) of an ADC. Assuming the quantization error is uniformly distributed between  $\pm LSB/2$ , the quantization error power is related to the quantization step:

$$e_q^2 = \frac{1}{LSB} \int_{-LSB/2}^{LSB/2} e_q^2 de_q = \frac{\Delta^2}{12}$$

(2.4)

Figure 2.9: (a) Characteristic transfer curve for multi-level quantization (b) Resulting error

The quantization error is dependent on the resolution of the ADC and it is often referred to as the quantization noise of an ADC. The quantizer can be modeled as a quantization noise source, shown in Figure 2.10. From the equation 2.4, the peak SNR of an ideal N bit ADC for a sinusoidal input signal can be calculated as shown in equation 2.5

$$SNR_p = 10\log(\frac{e_s^2}{e_q^2}) = 6.02N + 1.76dB$$

(2.5)

where  $e_s^2$  is the maximum input signal power. Here equation 2.5 gives the best possible SNR for a N-bit ADC.

### 2.4.3 Quantization Noise

The noise resulting from the quantization process is called the quantization noise and it is independent of the input signal. Moreover, the quantization noise power spectral density  $S_e(f)$  is white and uniformly distributed in the sampling frequency band  $\pm f_s/2$ , where  $f_s$  is the sampling frequency. The total quantization power is  $\Delta^2/12$ , so the amplitude of the power spectral density is:

$$h_e = \left\lceil \frac{\Delta^2}{12} \right\rceil \frac{1}{f_s} \tag{2.6}$$

as shown in Figure 2.11. The total power of the quantization noise is evenly distributed within  $\pm f_s/2$ . As the sampling frequency increases, the amplitude of the spectral density decreases, but the total quantization noise power remains the same.

Figure 2.10: Linear model of a quantizer

# 2.5 Oversampling $\Sigma \triangle$ ADCs : Fundamentals

In contrast to Nyquist-rate ADCs, oversampling  $\Sigma\Delta$  converters make use of two key techniques to decrease the quantization error power within the signal band and increase the accuracy of the A-to-D conversion. These techniques are oversampling and noise shaping (76).

Figure 2.11: Power spectral density of quantization noise

#### 2.5.1 Oversampling

Oversampling consists of sampling a signal faster than Nyquist rate- the minimum sampling frequency required to avoid aliasing. How much faster than required the signal is sampled is expressed through the oversampling ratio, defined as the ratio between the sampling frequency and the Nyquist frequency.

$$OSR = \frac{f_s}{f_n} = \frac{f_s}{2f_B} \tag{2.7}$$

In an oversampled converter, the power of the quantization error is uniformly distributed across the sampling frequency  $-f_s/2$  to  $+f_s/2$ , but only a part of the total error falls within the signal band, as long as  $f_s > 2f_B$  as shown in Figure 2.12. A low-pass decimation filter can be used to eliminate the quantization noise that falls outside the signal band  $f_B$ . Thus the quantization noise power is reduced to equation 2.8.

$$P_e = \int_{-f_s/2}^{f_s/2} S_e(f) |H(f)|^2 df = \left(\frac{\Delta^2}{12}\right) \frac{1}{OSR}$$

(2.8)

Therefore, by using an oversampling technique, the quantization noise power of an ADC can be reduced by a factor of OSR. It is an effective way to increase

Figure 2.12: PSD of the quantization error in an oversampled converter. Total power of the quantization error and power within the signal band are highlighted

the SNR, and hence the resolution, of an ADC system. Therefore, the peak SNR now is given by equation 2.9

$$SNR_p = 10\log(\frac{e_s^2}{P_e}) = 6.02N + 1.76 + 10\log(OSR)dB$$

(2.9)

This formula clearly shows the benefit of oversampling. For example, the peak SNR of an ADC can be increased by 3 dB by doubling the sampling frequency, i.e. the resolution of the ADC increases by 0.5 bit/octave. Therefore, an increase in OSR augments the effective resolution of the converter, but reduces the maximum signal frequency that can be processed. So, in an oversampling converter, signal bandwidth and accuracy are exchanged.

## 2.5.2 Noise-shaping

An approach to further increase the accuracy of the A-to-D conversion is through noise shaping. Noise-shaping implies filtering of the quantization errors, in order to shape their frequency response. As a result, the quantization error power is reduced in the frequency band of interest, while it is increased outside that band as shown in Figure 2.13. In this way, high resolution can be obtained in a relatively small bandwidth (75).

Figure 2.13: Noise shaping characteristics of  $\Sigma \triangle$  ADC

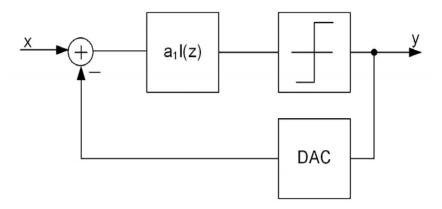

By applying a loop filter H(f) before the quantizer and introducing the feedback, shown in Figure 2.14, a  $\Sigma\Delta$  modulator can be constructed and different signal and quantization noise transfer functions is realized. After the decimation, the in-band quantization noise power is greatly suppressed. While combining with oversampling and noise shaping, a significant SNR improvement can be achieved for a  $\Sigma\Delta$  ADC compared to the ADC with oversampling only.

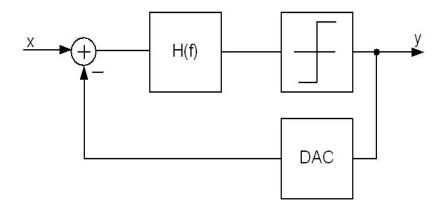

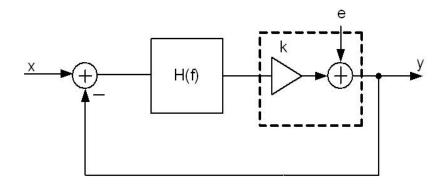

The basic  $\Sigma\Delta$  modulator is shown in Figure 2.15 and its linear model is shown in Figure 2.16. The basic  $\Sigma\Delta$  modulator consists of a loop filter, a quantizer and a feedback loop. Since the output of the quantizer is a digital signal, a digital to analog converter (DAC) is placed in the feedback path. The linear model of a  $\Sigma\Delta$  modulator models the quantizer with a quantization gain k and a noise source. It is assumed that the DAC inside the feedback loop is an ideal one. In this system, there are two input signals, x(n) and e(n), and one output signal

Figure 2.14: Block diagram of a noise shaping ADC system

y(n). The output of the  $\Sigma \triangle$  modulator can be expressed as in equation 2.10:

$$Y(z) = H_x(z)X(z) + H_e(z)E(z)$$

(2.10)

where  $H_x(z)$  represents the signal transfer function and  $H_e(z)$  represents the quantization noise transfer function in the domain. The signal and noise transfer function can be calculated as in equations (2.11-2.12):

$$H_x(z) = \frac{H(z)}{1 + H(z)}$$

(2.11)

$$H_e(z) = \frac{1}{1 + H(z)} \tag{2.12}$$

By properly choosing the loop filter transfer function H(z), the desired signal and noise transfer function can be obtained. For example, if an integrator is chosen to be the loop filter, its transfer function is given in equation 2.13:

$$H(z) = \frac{z^{-1}}{1 - z^{-1}} \tag{2.13}$$

Figure 2.15: Block diagram of a  $\Sigma\triangle$  modulator

Figure 2.16: Linear model of a  $\Sigma\Delta$  modulator

Then the signal and noise transfer functions of the  $\Sigma \triangle$  modulator can be calculated as in equation 2.14-2.15:

$$H_x(z) = z^{-1} (2.14)$$

$$H_e(z) = 1 - z^{-1} (2.15)$$

Substituting equations 2.14 and 2.15 in equation 2.10, the general expression for a first-order low-pass  $\Sigma\Delta$  modulator is obtained as in equation 2.16:

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})E(z)$$

(2.16)

The equation 2.16 indicates that the signal can pass the  $\Sigma\Delta$  modulator directly with a unit delay  $z^{-1}$  and the quantization noise has a high-pass characteristics 1- $z^{-1}$ , allowing noise suppression at low frequencies (74).

### 2.6 $\Sigma \triangle$ Modulator

The  $\Sigma\Delta$  modulator is a feedback system. In the time domain, the integrator integrates the difference between the input signal and the feedback output signal of the  $\Sigma\Delta$  modulator. The result of the integrator is then fed to the quantizer (79). The negative feedback tries to minimize the difference between the input signal and the output signal of the  $\Sigma\Delta$  modulator. As a result, the average of the output signal of the  $\Sigma\Delta$  modulator is tracking the input signal. This behavior is illustrated in Figure 2.17.

It can be seen that the output of the  $\Sigma\triangle$  modulator tracks the input signal. In Figure 2.17a, a single-bit quantizer is used in the  $\Sigma\triangle$  modulator. The benefit of using a single-bit quantizer is that the linearity of a single-bit quantizer is assured. Since there are only two output states in the single-bit quantizer and two points define a straight line, so the single-bit quantizer is inherently linear. Therefore the single bit quantizer is widely used in oversampled ADCs. The multi-bit quantizer generates less quantization noise power compared to the single-bit quantizer, as shown in Figure 2.17b. As a result the average value of the output tracks the input signal much closer than the single-bit one.

So far we have discussed low-pass  $\Sigma \triangle$  modulators. Depending on the frequency band of interest, there is another type of  $\Sigma \triangle$  modulator, band-pass  $\Sigma \triangle$  modulator, widely used in wireless transceivers. By applying different loop filters inside the  $\Sigma \triangle$  modulator, a high attenuation of quantization noise in a certain frequency band can be realized. For example, when the loop filter is of second-order given by equation 2.17:

$$H(z) = \frac{-z^2}{1+z^{-2}} \tag{2.17}$$

Figure 2.17: (a)Input and output waveforms of a first-order  $\Sigma \triangle$  modulator with single-bit quantizer (b) Output waveform of a first-order  $\Sigma \triangle$  modulator with multi-bit quantizer

Then the signal and noise transfer functions of the  $\Sigma\triangle$  modulator is given by equations 2.18 and 2.19

$$H_x(z) = -z^2 (2.18)$$

$$H_e(z) = 1 + z^{-2} (2.19)$$

The output spectrum of a bandpass  $\Sigma\Delta$  modulator is shown in Figure 2.18. The quantization noise is suppressed in the frequency band around  $f_s/4$ . This type of modulator is useful in digitizing signals within a certain frequency range and find its applications in wireless transceivers.

Figure 2.18: Output spectrum of a bandpass  $\Sigma \triangle$  modulator

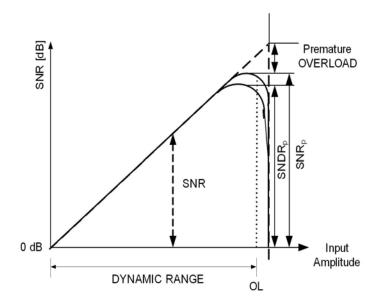

### 2.7 Performance Metrics for the $\Sigma \triangle$ ADC

For oversampled ADCs, since the operation principles are different from the Nyquist ADCs, different performance metrics are used to evaluate the performance of oversampled ADCs. Some important specifications are discussed here.

Signal to Noise Ratio (SNR) The SNR of a converter is the ratio of the input signal power to the noise power measured at the output of the converter. The maximum SNR of a converter can achieve is called peak signal-to-noise-ratio (SNRp). The noise here include the quantization noise and circuit noise.

Signal to Noise and Distortion Ratio (SNDR) The SNDR of a converter is the ratio of the input signal power to the power of the distortion components and noise measured at the output of the converter. The maximum SNDR of a converter can achieve is called peak signal-to-noise-and-distortion-ratio (SNDRp).

#### Dynamic Range (DR)

The DR is the ratio between the maximum input signal power can be applied to the input of the converter without significant performance degradation, and the minimum detectable input signal power. A significant performance degradation of a converter is considered as the SNR drops more than 3 dB below the peak SNR value. The minimum detectable input signal is the input power that the converter has for a SNR of 0 dB.

Overload Level The OL is the relative input amplitude where the SNR decreases by 3 dB below the peak SNR.

Spurious Free Dynamic Range (SFDR) The SFDR is defined as the ratio of the power of the signal to the power of the highest harmonic or spurious noise component. SFDR gives an indication of how far below the signal it is possible to go without hitting any noise or distortion.

**Total Harmonic Distortion (THD)** The total harmonic distortion (THD) is defined as the ratio of the total harmonic distortion power and the power of the fundamental frequency of the signal. THD is normally calculated for a certain number of harmonics.

The figure 2.19 shows the SNR and SNDR of the  $\Sigma\Delta$  modulator versus the amplitude of the signal applied to the input of the converter. Naturally, the SNR increases linearly with the increase of the input amplitude for an ideal converter. When the input signal amplitude is small, the distortion component is immersed in the noise floor of the converter. Therefore, the SNR and SNDR curves are merged together. With the increase of the input amplitude, the distortion power becomes larger than the noise power and the SNDR starts to decrease. The SNDRp reflects the linear performance of the converter. Due to the distortion power, the SNDRp is smaller than the SNRp for the same converter. After the converter reaches its SNRp, the performance of the converter degrades drastically due to the overload of the modulator, where instability occurs. The overload is the special characteristics of the  $\Sigma\Delta$  modulator. The overload level of a  $\Sigma\Delta$  modulator defines the dynamic range of a converter. When the input amplitude

is larger than a certain value, the  $\Sigma\Delta$  modulator loop becomes unstable and the noise shaping disappears. Large quantization power in the signal band results into a drastic decrease of the SNR. In the normal operation of the  $\Sigma\Delta$  modulator, overload should be avoided.

Figure 2.19: Definitions of the performance metrics used to characterize a  $\Sigma \triangle$  ADC

# 2.8 Traditional $\Sigma \triangle$ ADC Topology

The  $\Sigma\triangle$  ADC trades speed with resolution by means of oversampling and noise shaping. In this section, the single-loop  $\Sigma\triangle$  modulator is introduced along with the relationship between the performance and the topology parameters. Then the cascaded  $\Sigma\triangle$  modulator is presented. To make a difference from the feed-forward topology introduced in Chapter 3, the  $\Sigma\triangle$  modulator topology without feedforward is called traditional topology.

## 2.8.1 Single-Loop Single-Bit $\Sigma \triangle$ modulators

The single-loop  $\Sigma \triangle$  converter is defined as there being only one single  $\Sigma \triangle$  loop in the whole converter. The ability of noise shaping can be improved by increasing

the order of the loop filter. Shown in Figure 2.20 is the block diagram of a first-order single-loop  $\Sigma\Delta$  modulator. By inserting another integrator inside the loop a second-order  $\Sigma\Delta$  modulator can be obtained as shown in Figure 2.21.

Figure 2.20: The first-order single-loop  $\Sigma \triangle$  modulator

Figure 2.21: The second-order single-loop  $\Sigma \triangle$  modulator